Received 1 June 2025, accepted 29 July 2025, date of publication 1 August 2025, date of current version 11 August 2025.

Digital Object Identifier 10.1109/ACCESS.2025.3595055

# **Current-Voltage Modeling of Transistors Based on Two-Dimensional Molybdenum Disulfide**

ADELCIO M. DE SOUZA<sup>®</sup>, DANIEL R. CELINO<sup>®</sup>, REGIANE RAGI<sup>®</sup>, AND MURILO A. ROMERO<sup>®</sup>, (Senior Member, IEEE)

Department of Electrical and Computer Engineering, São Carlos School of Engineering, Universidade de São Paulo, São Carlos 13566-590, Brazil Corresponding author: Murilo A. Romero (murilo.romero@usp.br)

This work was supported in part by the Conselho Nacional de Desenvolvimento Científico e Tecnológico under Grant 309343/2021-6 and Grant 402081/2023-4; in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior; and in part by the Fundação de Amparo à Pesquisa do Estado de São Paulo under Grant 2018/13537-6, Grant 2021/06569-1, and Grant 2024/04319-6.

**ABSTRACT** This paper presents a compact model for the current-voltage (I–V) characteristics of field-effect transistors (FETs) based on two-dimensional molybdenum disulfide (MoS<sub>2</sub>) channels. The proposed model is fully analytical, explicit, and physics-based, ensuring compatibility with circuit simulators while providing a comprehensive description of the device behavior. A key starting point is the derivation of a closed-form expression for the electrostatic potential, achieved through a novel solution of the Poisson equation, by means of a Taylor series expansion method using a sliding expansion point. Our modelling approach avoids iterative procedures and special functions commonly used in the literature and allows a more detailed and physically grounded analysis of device operation into a unified analytical framework, including effects often overlooked or fragmented in previous works, as the model incorporates critical non-idealities, such as short-channel effects, interface traps, carrier mobility degradation, and velocity saturation. The results are validated against experimental and simulation data from the literature, demonstrating excellent agreement. This work offers a robust and accessible modeling approach for 2D-FETs, enabling the design of high-performance integrated circuits and favoring the practical implementation of two-dimensional materials in nanoelectronics.

**INDEX TERMS** Nanotransistors, molybdenum disulfide, compact model, analytical model, two-dimensional materials.

### I. INTRODUCTION

The aspects of band theory related to graphite have been known since 1947, through the pioneering work of Wallace [1]. The possibility of isolating a single layer of the material was also predicted by Boehm as early as 1962 [2]. Nevertheless, it was only in mid-2004 that Novoselov et al. experimentally demonstrated the material that became known as graphene [3]. From the outset, this material exhibited remarkable properties for microelectronics, such as extremely high carrier mobility, as well as a promise of improved electrostatic control due to the atomic thickness of the channel layer [4]. Thus, graphene was immediately seen as a strong candidate to replace silicon as the main material for high-performance transistors.

However, this groundbreaking material displays a zero bandgap, as demonstrated early on (see note 18 of [3]). The

The associate editor coordinating the review of this manuscript and approving it for publication was Ye Zhou .

presence of a bandgap is crucial for digital electronics applications, as it strongly affects the ON-OFF current ratio. In any case, despite this shortcoming, the discovery of graphene stimulated research groups worldwide to seek other materials, beyond carbon, which could also be isolated in one or a few layers [5]. What followed was the discovery and synthesis of a large variety of two-dimensional materials. Among these, molybdenum disulfide (MoS<sub>2</sub>) stands apart as a material with a direct bandgap of 1.8 eV in its two-dimensional form. The first MoS<sub>2</sub>-based transistor was demonstrated in 2011, registering an electron mobility of 200 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and an ON-OFF ratio of  $10^8$  [6]. Since then, MoS<sub>2</sub> has been one of the most investigated two-dimensional materials for nanoelectronics.

Regarding practical applications, a significant portion of early field-effect transistors based on two-dimensional materials (2D-FETs) were back-gate devices where the channel material was obtained by mechanical exfoliation, revealing the immature state of manufacturing

processes. More recently, significant advances in the growth techniques of these materials have been registered [7], and several integrated circuits based on 2D-FETs have been demonstrated [8]. Thus, it is expected that 2D-FETs with a structure similar to conventional metal-oxide-semiconductor field-effect transistors (MOSFETs) will start to boost high-performance integrated circuits and other applications in the next decade [9], [10].

In this framework, developing compact models able to capture the unique characteristics of  $MoS_2$ -based transistors becomes crucial. Several analytical or semi-analytical treatments have been proposed in the past [11], [12], [13], [14], [15], [16], [17]. However, many of these formulations require iterative procedures to solve transcendental equations. Other approaches use special functions or require the numerical solution of integrals, which is inconvenient for application in integrated circuit simulators. Furthermore, few works incorporate important non-idealities to ensure the robustness and accuracy of the proposed models.

Our work aims to contribute to the compact modeling of transistors based on molybdenum disulfide by providing a fully analytical, explicit, and physics-based framework. A core novelty lies in the derivation of a novel closed-form solution of the Poisson equation in the channel, obtained by means of a Taylor series expansion method with a sliding reference point. From this electrostatic potential expression, our approach builds up a fully analytical and easy to understand model, providing excellent agreement with numerical solutions. Our model also unifies several critical non-idealities, such as interface traps, short-channel effects, mobility degradation, and velocity saturation, into a single analytical formulation. A more detailed treatment of the device physics is also provided, consolidating aspects that are often dispersed in previous works.

The text is structured as follows: Section II discusses the relevant properties of transition metal dichalcogenides, a family of materials that includes molybdenum disulfide. Section III presents the device and its electrostatic modeling, including the analysis of carrier concentration, conduction band diagram, and approximate analytical solutions for the Poisson equation considering long-channel and shortchannel devices. Semiconductor defects such as interface traps and their influence on electrostatic control are also discussed. Section IV describes the current characteristics in the drift-diffusion regime, including the effects of carrier mobility degradation and carrier velocity saturation. In Section V, we validate the model considering experimental and simulation data available in the literature, covering all characteristics discussed earlier. Finally, we draw our conclusions in Section VI.

## **II. TRANSITION METAL DICHALCOGENIDES**

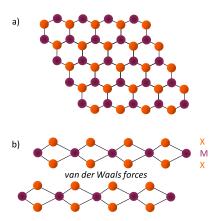

Transition metal dichalcogenides (TMDs) are layered materials composed of an  $MX_2$ -type structure, where M is a transition metal atom, and X is a chalcogen atom (sulfur, selenium, or tellurium). These materials can also be isolated

FIGURE 1. Typical crystal structure of two-dimensional transition metal dichalcogenides. a) Top view. b) Side view of two layers, where M is a transition metal atom, and X is a chalcogen atom. In the case of MoS<sub>2</sub>, M is Mo (molybdenum), and X is S (sulfur).

in single or few-layers configurations. In a monolayer configuration, the atoms are arranged in a hexagonal crystal lattice through covalent bonds, while in the transverse plane, they form an X-M-X arrangement. As a result, the thickness of a single layer of these compounds is approximately 0.65 nm, with subsequent layers bonded by weak van der Waals forces. Fig. 1 illustrates the typical structure of a 2D TMD.

About a year after the discovery of graphene, Novoselov et al. [18] also demonstrated two-dimensional forms of molybdenum disulfide (MoS<sub>2</sub>) and niobium diselenide (NbSe<sub>2</sub>), with the former being a semiconductor and the latter a semimetal. However, the measured carrier mobilities were disappointedly low, between 0.5 and 3 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, revealing that these early experiments were far from exploring the maximum potential of these materials.

Later, in 2010, it was experimentally demonstrated that two-dimensional MoS<sub>2</sub> is a direct bandgap semiconductor, unlike its bulk form [19]. Fabrication processes had evolved and, in the same year, Radisavljevic et al. [6] produced the first transistor based on a single layer of MoS<sub>2</sub>. Using hafnium dioxide (HfO<sub>2</sub>) as the gate oxide, they achieved an electron mobility of 200 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, higher than achieved for ultrathin (i.e., less than 5 nm) silicon films. Since monolayer MoS<sub>2</sub> has a bandgap of 1.8 eV, the current ON-OFF ratio reaches levels as high as 10<sup>8</sup>, which is quite suitable for digital microelectronics.

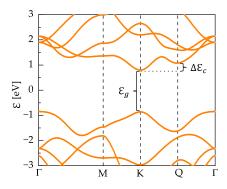

The two-dimensional form of  $MoS_2$  has a direct bandgap at the K point of the first Brillouin zone. In addition, it presents a second valley in the conduction band, at a slightly higher energy than the primary valley. This second valley is located at the Q point, an intermediate to the K and  $\Gamma$  points, and computational calculations indicate that it significantly contributes to the total current of  $MoS_2$ -based 2D-FETs [20]. Fig. 2 shows the band structure of  $MoS_2$  monolayers as obtained by *ab initio* methods [21], [22], highlighting the energy difference  $\Delta \mathcal{E}_c$  between the two main valleys in the conduction band and the bandgap.

**FIGURE 2.** Band structure of monolayer MoS $_2$  calculated from *ab initio* methods. [21], [22]. The material presents two valleys in the conduction band, both significantly contributing to the carrier density. The primary valley is at the K point (direct bandgap,  $\mathcal{E}_g$ ), while the secondary valley is at the Q point within the first Brillouin zone. The energy difference between both is denoted as  $\Delta\mathcal{E}_c$ . In our model, we assume  $\mathcal{E}_g=1.8$  eV and  $\Delta\mathcal{E}_c=0.1$  eV. Also, both valleys present near-parabolical shapes, so the effective mass approximation is adopted with  $m_K^*=0.457m_0$  and  $m_O^*=0.543m_0$ .

These features are considered when calculating the density of states. Assuming a parabolic approximation for the dispersion relation, the density of states is given by [12]

$$g_{2D}\left(\mathcal{E}\right) = \sum_{\ell} \left(\frac{g_s g_{\ell} m_{\ell}^*}{2\pi \hbar^2}\right) \ell = 1, 2, \dots \tag{1}$$

where  $\hbar$  is the reduced Planck's constant,  $g_s=2$  is the degeneracy factor due to spin,  $g_\ell$  and  $m_\ell^*$  are, respectively, the degeneracy factor and the effective mass corresponding to the  $\ell^{\text{th}}$  valley considered. Given the crystal lattice structure of MoS<sub>2</sub>, we have  $g_K=2$  and  $g_Q=6$ , which also increases the contribution of the secondary valley to the current composition.

## III. ELECTROSTATIC MODELING

The initial stage of our modeling consists of establishing a charge-control relation between the carrier concentration in the channel and the voltage applied to the gate terminal, in the absence of current flow. In this context,  $V_{ds} = 0$ , and the potential of the Fermi level along the channel is fixed as an invariant reference value expressed as V.

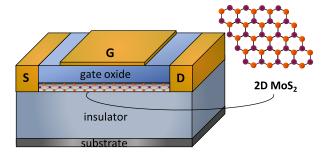

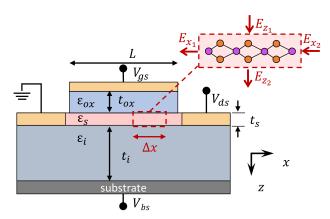

The device to be modeled is presented in Fig. 3. From bottom up, it comprises a substrate, usually made of highly doped silicon, and an insulator, typically thermally-grown silicon dioxide. The two-dimensional semiconductor (MoS<sub>2</sub>) channel is placed on top of the insulator, with the gate oxide located above it. As in state-of-the-art transistors, this gate oxide can be made of silicon dioxide or some other insulating material with a high dielectric constant. Finally, the source, drain, and gate contacts are made of metals.

Since the first demonstration, transistors fabricated with MoS<sub>2</sub> channels have been known to be naturally n-type, favoring electron conduction, regardless of the number of layers or the type of metal used in the contacts [6]. Recently, this behavior has been attributed to unintentional carbon doping

FIGURE 3. Three-dimensional schematic of a 2D-FET with a MoS<sub>2</sub> channel.

of the  $MoS_2$  samples [23]. Therefore, in this work, an n-type device is assumed, with a donor density,  $N_D$ , given in cm<sup>-2</sup>.

### A. CARRIER CONCENTRATION

The electron concentration in the two-dimensional channel is given by:

$$n_{2D} = \int_{\mathcal{E}_c}^{\infty} g_{2D}(\mathcal{E}) f(\mathcal{E} - \mathcal{E}_F) d\mathcal{E}, \qquad (2)$$

In the above equation,  $f(\mathcal{E} - \mathcal{E}_F)$  is the Fermi-Dirac distribution, where  $\mathcal{E}_F$  the Fermi level energy. Regarding the integration limits, the conduction band of the MoS<sub>2</sub> channel consists of discrete levels. However, carriers are confined within a thickness of  $\sim$ 1 nm and these levels are widely spaced, in such way that only the first energy level needs to be taken into account, because it will be the only significantly occupied by electronic carriers. This first energy sub-band corresponds to the bottom of the conduction band for the MoS<sub>2</sub> channel and will be denoted as  $\mathcal{E}_c$  in the remainder of this paper.

In order to calculate the carrier concentration, we assume  $\mathcal{E}_c = -q\varphi$ , where  $\varphi$  is the channel electrostatic potential energy. Also,  $\mathcal{E}_F = -qV$ , as mentioned earlier. Thus, assuming the Boltzmann approximation to solve eq. (2), we have:

$$n_{2D} = N_{\text{DoS}} \exp\left(\frac{\varphi - V}{\phi_{\text{T}}}\right),$$

(3)

where

$$N_{\rm DoS} = \frac{g_K m_K^* k_B T}{\pi \hbar^2} + \frac{g_Q m_Q^* k_B T}{\pi \hbar^2} \exp\left(-\frac{\Delta \mathcal{E}_c}{k_B T}\right), \quad (4)$$

and  $\phi_T = k_B T/q$  is the thermal voltage, where  $k_B$  is the Boltzmann constant, and T is temperature.

The doping level in MoS<sub>2</sub> transistors is generally quite low, on account of the difficulties of intentional doping in two-dimensional semiconductors. Also, as Cao et al. [12] pointed out, the high density of states in MoS<sub>2</sub> makes the channel potential less dependent on the gate voltage. In other words, it prevents the Fermi level from deeply entering the conduction band, which could lead the semiconductor to a degenerate state. All factors considered, the Boltzmann approximation provides an accurate description for the carrier concentration.

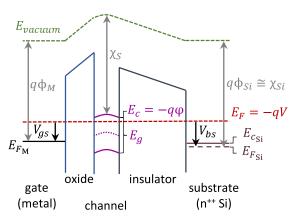

**FIGURE 4.** Conduction band diagram of a 2D-FET, where a highly doped n-type silicon substrate is assumed. The device is biased with  $V_{gs} > V_{FB}$ , as evidenced by the bending of the conduction band in the semiconductor channel region.

# B. CONDUCTION BAND PROFILE

Fig. 4 shows the conduction band energy profile for a 2D-FET. From top to bottom (i.e., left to right in the figure), we first have the metal gate contact, characterized by the work function  $\phi_M$  [eV]. The applied gate voltage ( $V_{gs}$ ) shifts the Fermi level at the metal contact with respect to the semiconductor. As a consequence, there is a potential drop across the gate oxide ( $\varphi_{ox}$ ) and the semiconductor channel, which is characterized by an electron affinity  $\chi_S$  [eV] and bandgap energy  $\mathcal{E}_g$ . The work function of the two-dimensional semiconductor can be calculated by:

$$\phi_S = \frac{\chi_S}{q} + \frac{\mathcal{E}_g}{2q} - \phi_T \ln \left( \frac{n_{2D}}{n_i} \right), \tag{5}$$

where  $n_i$  is the intrinsic electron concentration. On account of the immature fabrication processes, the doping densities are rather low in these devices, in such way that  $n_{2D} \cong n_i$  at flatband condition, thereby placing the Fermi level in the semiconductor near the mid-gap. Accordingly, even if a slightly higher intentional doping level is assumed in the source and drain regions, these 2D-FETs will be accumulation-type transistors. Specifically, they operate in a carrier depletion regime in the off-state and a carrier accumulation regime in the on-state [24], in a very similar way to junctionless transistors [25]. The flatband voltage is defined from the diagram simply as  $V_{FB} = \phi_{MS}$ .

Moving forward, we reach the substrate insulator. It should be stressed that the diagram in Fig. 4 is not on scale. While the 2D channel typically has a thickness of  $\sim$ 1 nm, the insulator thickness is on the order of hundreds of nanometers. Finally, the substrate is usually made of highly doped silicon. In this case, n-type doping is assumed so that the work function of silicon is approximately  $\chi_{Si}/q$ . A fixed voltage  $V_{bs}$  can be applied to the substrate to shift the Fermi level and, consequently, alter the electrostatic characteristics of the transistor. For instance, this technique is often used in MOSFETs to adjust the threshold voltage. For 2D-FETs, it can also be

FIGURE 5. Schematic for electrostatic analysis of a 2D-FET. A region of infinitesimal width, where Gauss law is applied, it is highlighted in the channel. The gate oxide, semiconductor, and insulator have thicknesses t and permittivities  $\varepsilon$  labeled with their respective subscripts.

used to provide the so-called electrostatic doping since the substrate extends to the region of the contacts.

## C. POISSON EQUATION

To establish the charge control relation, it is first necessary to write the Poisson equation governing this device. Fig. 5 shows the scheme proposed initially by Cao et al. [12] to analyze the electric field  $\vec{E}$  in an infinitesimal section of the channel  $(\Delta x)$ , by using Gauss law.

In this two-dimensional representation, the gate voltage is applied along the *z*-axis, and the current flow occurs in the *x*-direction. Consequently, there is no potential difference applied along the *y*-axis, parallel to the cross-section of the device. Given that there is no electric field applied along the *y*-direction and that the channel is formed by just a few layers of MoS<sub>2</sub>, it is fair to assume that  $\varphi(x, y, z) \approx \varphi(x)$  in the channel.

The Poisson equation for this device is then written as

$$\frac{d^{2}\varphi(x)}{dx^{2}} - \frac{\varphi(x)}{\lambda^{2}} + \frac{C_{ox}\left(V_{gs} - V_{t}\right)}{\varepsilon_{s}t_{s}}$$

$$= \frac{qN_{DoS}}{\varepsilon_{s}t_{s}} \exp\left[\frac{\varphi(x) - V(x)}{\phi_{T}}\right], \tag{6}$$

where  $C_{ox} = \varepsilon_{ox}/t_{ox}$  is the oxide capacitance, and  $\lambda$  is the characteristic length of the 2D-FET, given by

$$\lambda = \sqrt{\frac{\varepsilon_s t_s t_{ox} t_i}{\varepsilon_{ox} t_i + \varepsilon_i t_{ox}}},\tag{7}$$

and  $V_t$  is the threshold voltage, given as

$$V_{t} = V_{FB} + \frac{C_{i} (V_{bs} - V_{i}) - qN_{D}}{C_{ox}},$$

(8)

where the term  $V_i$  corresponds to the difference between the work functions of the semiconductor and the substrate, and  $C_i = \varepsilon_i/t_i$  is the capacitance of the insulator.

Once the Poisson equation governing the electrostatic behavior of the device is established, the next step towards a full description of the I–V characteristics is to obtain an

analytical solution for the electrostatic potential along the channel. The analysis is carried out considering two distinct cases. In the first, the device is long enough to allow the gradual channel approximation. In the second case, we account for short-channel effects, which may lead to degraded electrostatic control.

#### D. ANALYTICAL SOLUTION FOR LONG-CHANNEL DEVICES

Considering the gradual channel approximation, one can take  $d^2\varphi(x)/dx^2=0$  in eq. (6). Thus, rearranging the terms, we have an implicit relationship between the electrostatic potential in the channel and the applied voltage at the gate contact:

$$(C_{ox} + C_i) \varphi(x) + qN_{DoS} \exp\left[\frac{\varphi(x) - V(x)}{\phi_{T}}\right]$$

$$= C_{ox} (V_{gs} - V_t). \tag{9}$$

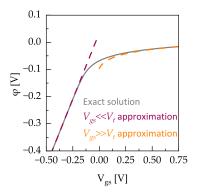

Eq. 9 is a transcendental equation for  $\varphi(x)$ , so it is necessary to introduce some analytical approximations to make it an explicit relation regarding the dependence of the channel potential with respect to the bias voltages. To do so, a useful first step is to know the asymptotic behavior of  $\varphi(x)$  for  $V_{gs} \ll V_t$  and  $V_{gs} \gg V_t$ .

In eq. (9), the first term on the left-hand side relates to the capacitive control of the channel by the gate contact, while the second term corresponds to the accumulated charge density. Without loss of generality, we can set V(x) = 0 to easy the analysis. For  $V_{gs} \ll V_t$ , the transistor operates in the subthreshold region, and  $n_s(x) \cong 0$ . Therefore, we have:

$$\varphi(x) \cong \frac{C_{ox}}{C_{ox} + C_i} \left( V_{gs} - V_t \right), \tag{10}$$

that is, the electrostatic potential of the channel varies linearly with the applied gate voltage.

As the gate voltage approaches the threshold value, the accumulated charge density grows exponentially. In the limit, when  $V_{gs} \gg V_t$ , we have:

$$\varphi(x) \cong \phi_{\rm T} \ln \left[ \frac{C_{ox}}{q N_{\rm DoS}} \left( V_{gs} - V_t \right) \right],$$

(11)

i.e., the potential grows less sharply with the applied gate voltage. Fig. 6 illustrates these asymptotic behaviors, when compared to the exact solution of eq. (9).

In order to solve the transcendental equations, such as eq. (9), and obtain an explicit analytical expression for the channel potential  $\varphi(x)$  as a function of the bias voltages, a usually employed technique is to expand the exponential term in eq. (9) into a Taylor series. Taking an arbitrary point  $\Phi$  as a reference, one gets:

$$\exp\left(\frac{\varphi}{\phi_{\rm T}}\right) \cong \exp\left(\frac{\Phi}{\phi_{\rm T}}\right) \sum_{j=0}^{n} \frac{1}{j!} \left(\frac{\varphi - \Phi}{\phi_{\rm T}}\right)^{j}. \tag{12}$$

The accuracy of this expansion within a given interval will primarily depend on two factors: the number of terms (n) retained in the approximation and the choice of the expansion

**FIGURE 6.** Asymptotic behavior of the electrostatic potential below and above threshold, respectively. Simulation parameters: monolayer  $MoS_2$  channel with  $N_D=3.5\times10^{11}~cm^{-2}$ ,  $SiO_2$  gate oxide and insulator with  $t_{OX}=5$  nm and  $t_i=90$  nm, Al gate, and  $n^{++}$  Si substrate.

point  $\Phi$ . Since the expansion results in a polynomial function, retaining n terms implies finding the roots of an  $n^{\text{th}}$ -degree polynomial, which can be quite difficult for n > 2.

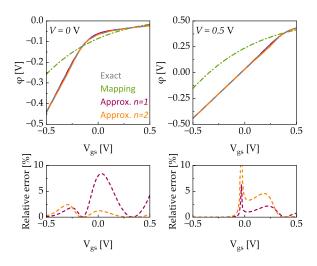

As an alternative, we have developed a new approach to solve transcendental equations, which we applied in the context of the compact modeling of ballistic 2D-FETs [26], [27], [28]. In this approach, we still use a Taylor series expansion, but employ a sliding expansion point  $\Phi$ , which is determined by a mapping function, obtained by inspecting the behavior of  $\varphi$  within a given interval.

Following this principle, a typical mapping function for  $\Phi(V_{gs})$  is

$$\Phi = 2\phi_T + \frac{2\left[\alpha \left(V_0 - V_t\right) - 2\phi_T\right]}{1 + \exp\left[d\left(V_{gs} - V_0\right)\right]},\tag{13}$$

where  $V_0$  and d are fixed parameters, and  $\alpha = C_{ox}/(C_{ox} + C_i)$ . The parameter  $V_0$  is dominant for  $V_{gs} \ll V_t$ , so it can be chosen, for instance, as  $V_0 = V_t - 1.65$ . Meanwhile, the parameter d determines the smoothness of the transition in the asymptotic behavior of  $\varphi$  as  $V_{gs} \approx V_t$ . In this case, choosing d = 2 results in a good match.

Moving forward with the analysis of eq. (9), our study indicated that, with the new approach, retaining just the first two terms of the expansion, eq. (12), is sufficient to achieve the desired accuracy. Thus, a fully explicit and analytical expression for  $\varphi(V_{gs})$  is written as

$$\varphi = \frac{qN_{\text{DoS}}\left(\Phi - \phi_{T}\right) \exp\left[\Phi/\phi_{T}\right] + \phi_{T}C_{ox}\left(V_{gs} - V_{t}\right)}{qN_{\text{DoS}} \exp\left[\Phi/\phi_{T}\right] + \phi_{T}\left(C_{ox} + C_{i}\right)}.$$

(14)

Fig. 7-a illustrates a typical example, providing excellent matching between the exact behavior and the proposed approximation, retaining only the first two terms in eq. (12). Even when only the first term is used, the relative error remains below 8.43% near the threshold voltage, already demonstrating fair accuracy. Otherwise, the accuracy can be further improved by keeping one more term (n=2) in eq. (12) and finding the roots of a second-degree polynomial.

FIGURE 7. Comparison between the exact solution and the approximate expression for the electrostatic potential considering n = 1 and n = 2. Specifications: monolayer  $MoS_2$  channel with  $N_D=3.5\times 10^{12}$  cm<sup>-2</sup>,  $HfO_2$  gate oxide ( $t_{ox}=2$  nm),  $SiO_2$  insulator ( $t_i=90$  nm), Cr gate, and  $n^{++}$  Si substrate. The respective mapping functions  $\Phi\left(\textit{V}_{\textit{gs}}\right)$  used for the calculations are also shown. a) V = 0 V. b V = 0.5 V.

In this case, for n = 2, the maximum relative error is only 2.41%.

In the more general, case where  $V(x) \neq 0$ , the same method can be applied. by considering the expansion variable as the difference  $\varphi(x) - V(x)$  and carrying the same analysis. Fig. 7-b depicts an analysis similar to the one discussed earlier, but now considering V = 0.5 V. In this case, the relative error is kept below 5% for most of the interval.

In summary, a fully analytical and explicit expression for  $\varphi(V_{es}, V_{ds})$  was obtained for long-channel transistors. As it will be shown later, from this analysis, it is possible to calculate the carrier density in the channel  $n_{2D}$  ( $V_{gs}$ ,  $V_{ds}$ ) and obtain an expression for the current characteristics.

# E. ANALYTICAL SOLUTION FOR SHORT-CHANNEL **DEVICES**

The gradual channel approximation is inappropriate for the modeling of very short gate-length transistors, which, in principle, require the solution of the Poisson equation in its full form. However, within the scope of electrostatics analysis for compact modeling, short-channel effects are mostly important in the subthreshold region, where they degrade the transistor behavior as well as alter the value of threshold voltage itself. Thus, it is possible to restrict the analysis of short-channel effects to a solution of the Poisson equation under total carrier depletion, i.e.,

$$\frac{d^2\varphi(x)}{dx^2} - \frac{\varphi(x)}{\lambda^2} + \frac{C_{ox}\left(V_{gs} - V_t\right)}{\mathcal{E}_s t_s} = 0.$$

(15)

The third term of the above equation corresponds to the channel potential under subthreshold condition, as written for long-channel devices, eq. (9). Replacing this term into eq. (15), we have a differential equation of the form:

$$\frac{d^2\varphi(x)}{dx^2} - \frac{\varphi(x) - \varphi_{\ell}}{\lambda^2} = 0, \tag{16}$$

where

$$\varphi_{\ell} = \frac{C_{ox}}{C_{ox} + C_i} \left( V_{gs} - V_{t\ell} \right). \tag{17}$$

The solution to equation (16), considering the boundary conditions, is:

$$\varphi(x) = \varphi_{\ell} + \frac{(V_{ds} - \varphi_{\ell}) \sinh\left(\frac{x}{\lambda}\right) - \varphi_{\ell} \sinh\left(\frac{L - x}{\lambda}\right)}{\sinh\left(L/\lambda\right)}.$$

(18)

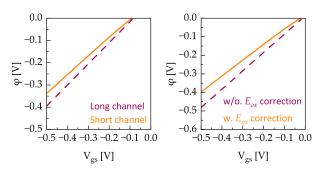

Hence, expression (18) describes the electrostatic potential for short-channel devices in the subthreshold region. Fig. 8-a compares the minimum value from eq. (9) to that of eq. (18) for a 2D-FET with L = 12 nm, revealing an important degradation of the subthreshold characteristics.

For compact modeling purposes, it should be noted that an expression for the current will depend on the integration of the term  $\exp[-\varphi(x)/\phi_T]$  over x [12]. Inspection of eq. (18) reveals that the integration must be carried out numerically. Therefore, it is imperative to obtain an approximation to allow an analytical treatment.

Keeping in mind that the subthreshold current characteristics are essentially dictated by the top of the potential energy barrier, a simple approach is to expand eq. (18) into a Taylor series around the point along the channel where the electrostatic potential is minimum, as it has been done for conventional MOSFETs [29]. Thus, the first step is to determine the expansion point, by taking the derivative of eq. (18) with respect to x and setting it to zero. The result is

$$x_{\min} = \frac{L}{2} - \frac{\lambda}{2} \ln \left[ \frac{(V_{ds} - \varphi_{\ell}) + \varphi_{\ell} \exp\left(-\frac{L}{\lambda}\right)}{-\varphi_{\ell} - (V_{ds} - \varphi_{\ell}) \exp\left(-\frac{L}{\lambda}\right)} \right]. \quad (19)$$

Then, we retain only the first two non-zero terms of the series, to write:

$$\varphi_{\text{approx}}(x) \approx A_2 (x - x_{\text{min}})^2 + A_0,$$

(20)

where  $A_i = \frac{d^i \varphi}{dx^i} (x = x_{\min})$ . For devices with very short channels (L < 30 nm), the lateral electric field in the oxide (i.e., the electric field component in the direction along the channel) also needs to be taken into account [12], [13]. In [13], the authors suggest a linear dependence relating the lateral electric field in the two-dimensional semiconductor  $E_x(x)$  to the lateral electric field in the oxide  $E_{ox}(x)$ , i.e.,  $E_x(x) = \alpha E_{ox}(x)$ , where  $\alpha$  is an empirical value obtained from TCAD simulations (Silvaco ATLAS). This approximation allows one to rewrite the characteristic length of the 2D-FET, eq. (7), to include the effect of the lateral electric field of the oxide, as:

$$\lambda = \sqrt{\frac{\mathcal{E}_s t_s t_{ox} t_i}{\mathcal{E}_{ox} t_i + \mathcal{E}_{itox}} + \frac{1}{\alpha} \left( \frac{\mathcal{E}_{ox} t_{ox}^2 t_i}{\mathcal{E}_{ox} t_i + \mathcal{E}_{itox}} \right)}.$$

(21)

Fig 8-b depicts the minimum value of the electrostatic potential when a high- $\kappa$  dielectric oxide (HfO<sub>2</sub>) is considered.

**FIGURE 8.** Value of the minimum electrostatic potential considering short-channel effects. Parameters: monolayer MoS<sub>2</sub> channel with  $N_D=3.5\times10^{11}~{\rm cm^{-2}}$  and  $L=12~{\rm nm}, V_{ds}=0.5~{\rm V}, {\rm SiO_2}$  insulator ( $t_i=90~{\rm nm})$  nm), Al gate, and n<sup>++</sup> Si substrate. a) Gate oxide: SiO<sub>2</sub> ( $t_{OX}=5~{\rm nm}$ ). b) Gate oxide: HfO<sub>2</sub> ( $t_{OX}=5~{\rm nm}$ ). A factor  $\alpha=0.96\varepsilon_{OX}/\varepsilon_{{\rm SiO_2}}$  was used, as done in [13].

While the oxide thickness and the other parameters are kept unchanged, it was necessary to account for the lateral electric field correction, in order to achieve a subthreshold behavior similar to the one registered with SiO<sub>2</sub> (Fig. 8-a). This indicates that the parasitic effect of the lateral field in the oxide is quite relevant for short-channel 2D-FETs, and its impact needs to be included for an accurate compact model.

## F. INTERFACE TRAPS

Although two-dimensional materials do not form chemical bonds out of the plane, interface traps can be induced by underlying materials or defects and impurities in the crystalline lattice. The problem is made worse by the present fabrication techniques for 2D-FETs, which lag far behind the state-of-the-art for silicon devices. As a consequence, today, even the best 2D-FETs will inevitably be affected by interface traps, especially considering the low density of states of these materials when compared to three-dimensional semiconductors.

In molybdenum disulfide, interface traps can arise from three main sources [30]: i) defects in the crystalline lattice, such as sulfur (S) vacancies; ii) defects in the substrate insulator or gate oxide; and iii) externally induced lattice strain.

Sulfur vacancies are relatively common when the material is grown by CVD and result in localized states near the middle of the bandgap ( $\mathcal{E}_{it} = \mathcal{E}_c - 0.46$  eV) [31]. Although the interface state density is typically high ( $10^{12}$  to  $10^{13}$  cm<sup>-2</sup>), the electrostatic control is not significantly altered. On the other hand, these point defects result in unintentional doping and reduce carrier mobility by increasing Coulomb scattering.

The substrate insulator often presents very few defects, as it typically consists of thermally oxidized silicon, a very mature technique. As such, the interface state density is on the order of  $10^{11}$  cm<sup>-2</sup> or lower. In contrast, depositing a gate oxide with a high dielectric constant onto a two-dimensional material is a challenge and often results in various defects. For instance, ultraviolet (UV) and ozone treatments are often used for surface preparation, and intermediate layers are frequently

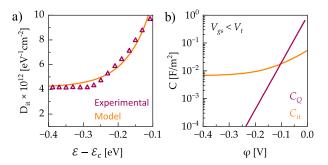

**FIGURE 9.** Analysis of the model to include interface trap effects. Parameters: monolayer MoS<sub>2</sub> channel, Al<sub>2</sub>O<sub>3</sub> gate oxide, SiO<sub>2</sub> insulator, Al gate, n<sup>++</sup> Si substrate,  $D_{it0} = 4.15 \times 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$ ,  $D_{it1} = 2.9 \times 10^{13} \text{ eV}^{-1} \text{ cm}^{-2}$  and  $\mathcal{E}_{\sigma} = 0.07 \text{ eV}$ . a) Validation of the expression for the interface states distribution compared against experimental data [30]. b) Comparison between the  $C_Q$  and  $C_{it}$  for  $V_{qs} < V_t$ .

employed to improve the interface quality between the oxide and the semiconductor. Also, the use of the atomic layer deposition (ALD) technique, at a relatively low temperature (200 °C), for oxide deposition, also introduces traps into the material [32].

Finally, as pointed out in various works by Fang et al. [30], [33], [34], the main source of interface states near the conduction band in MoS<sub>2</sub> is externally induced lattice strain. This occurs because the bandgap formation in this material is mainly due to the separation of d orbitals in molybdenum, which contributes to both the conduction and valence bands. As the material is extremely thin, slight roughness or defects in adjacent insulators can locally distort the chemical bond between molybdenum and sulfur, altering the band structure. Consequently, interface traps with a U-shaped distribution appear within the bandgap.

The conjunction of all these factors can be modeled by the expression for the distribution of interface states near the conduction band, which behave as acceptors:

$$D_{it}(\mathcal{E}) = D_{it0} + D_{it1} \exp\left(-\frac{\mathcal{E}_{c} - \mathcal{E}}{\mathcal{E}_{\sigma}}\right), \qquad (22)$$

where  $D_{it0}$  is a fixed parameter,  $D_{it1}$  is the peak value, and  $\mathcal{E}_{\sigma}$  determines the decay rate of the exponential. Fig. 9-a illustrates the validation of this model with the experimental data presented by Fang et al. [30].

The impact of interface traps can be included in the model for the channel potential by considering that a fraction of the carrier density  $n_{it}(x)$  occupies these interface states, according to the position of the Fermi level [12]. However, this approach significantly complicates the process of obtaining an explicit analytical expression for  $\varphi(V_{gs})$ .

For compact modeling purposes, Xu et al. [35] noted that the effects of interface traps on the electrostatic potential are significant only in the subthreshold region. Under this bias condition, the Fermi level is far from the bottom of the conduction band, and  $D_{it0}$  is the dominant term in eq. (22).

Therefore, it is convenient to consider a uniform distribution with an effective value,  $D_{it}(\mathcal{E}) = \overline{D_{it}}$ . Then, we have a capacitance due to interface traps given as  $C_{it} = q^2 \overline{D_{it}}$ , and the channel potential in the subthreshold region is rewritten as

$$\varphi(x) \cong \frac{C_{ox}}{C_{ox} + C_i + C_{it}} \left( V_{gs} - V_t \right), \tag{23}$$

This approximation is justified by contrasting  $C_{it}$  with the quantum capacitance, defined as

$$C_Q = q \frac{\partial n_{2D}}{\partial \varphi} = \frac{q^2 N_{DoS}}{k_B T} \left[ \frac{\exp\left(\frac{\varphi - V}{\phi_T}\right)}{1 + \exp\left(\frac{\varphi - V}{\phi_T}\right)} \right], \quad (24)$$

where Fermi-Dirac distribution was considered for improved accuracy. Also known as electrochemical capacitance [36],  $C_Q$  is directly associated with the two-dimensional density of states and represents the filling of discrete energy levels in the conduction band as a function of the applied voltage.

Fig. 9-b shows a comparison between the two capacitances for  $V_{gs} < V_t$ . The quantum capacitance grows exponentially with  $\varphi$  and exceeds  $C_{it}$ , which has an almost invariant behavior when  $V_{gs} \ll V_t$ . In [30], the authors suggest that  $\overline{D_{it}} = 8 \times 10^{12} \, \mathrm{eV^{-1} cm^{-2}}$  is able to reproduce the experimentally measured subthreshold slope a device fabricated with a 1 nm thick layer of yttrium oxide (Y<sub>2</sub>O<sub>3</sub>) used as a buffer layer to easy the deposition of the Al<sub>2</sub>O<sub>3</sub> layer onto MoS<sub>2</sub> and improve the interface quality.

## IV. MODELING OF I-V CHARACTERISTICS

For the modeling the I–V characteristics, the expression for the drain current can be directly written as a function of the electrostatic potential [12] or as a function of the charge in the channel [17], which is a function of the electrostatic potential. In both cases, our approach results in fully analytical expressions. However, the second option is the one that provides the best results, free from numerical errors.

## A. DRIFT-DIFFUSION FORMALISM

The I–V characteristics of the 2D-FET considering carrier transport governed by the drift-diffusion formalism are obtained by solving the following integral:

$$I_{ds} = \frac{qW}{L} \int_{0}^{V_{ds}} \mu n_{2D} dV, \qquad (25)$$

where the carrier mobility may initially be taken as  $\mu = \mu_0$ , a constant value.

Considering the gradual channel approximation, an expression for the Fermi level potential as a function of the channel potential is derived from eq. (9):

$$V = \frac{\lambda^2}{\mathcal{E}_s t_s} \left[ C_{ox} \left( V_{gs} - V_t \right) - q n_s \right] - \phi_T \ln \left( \frac{n_{2D}}{N_{DoS}} \right). \quad (26)$$

It is convenient to change the variables in the integral of eq. (25):

$$I_{ds} = \frac{qW\mu_0}{L} \int_{n_S}^{n_D} n_{2D} \frac{dV}{dn_{2D}} dn_{2D}, \tag{27}$$

where  $n_S = n_{2D} (V = 0)$ ,  $n_D = n_{2D} (V = V_{ds})$  and

$$\frac{dV}{dn_{2D}} = -\frac{q\lambda^2}{\varepsilon_s t_s} - \frac{\phi_{\rm T}}{n_{2D}}.$$

(28)

Solving the integral yields an expression for the I–V characteristics of a single-gate long-channel device, initially neglecting deleterious effects:

$$I_{ds} = -\frac{qW\mu_0}{L} \left[ \phi_{\rm T} \left( n_D - n_S \right) + \frac{q\lambda^2}{\varepsilon_S t_S} \left( n_D^2 - n_S^2 \right) \right]. \quad (29)$$

Since the carrier concentration depends only on the electrostatic potential and that this expression for the electrostatic potential can be explicitly obtained using the technique presented in the previous section, the I–V characteristics can also be calculated without the aid of numerical routines, which is an attractive feature for integrated circuit simulators.

# B. SUBTHRESHOLD CURRENT CONSIDERING SHORT-CHANNEL EFFECTS AND INTERFACE TRAPS

Analyzing only the subthreshold regime, eq. (25) can be solved with the aid of eq. (10):

$$I_{ds} = \frac{W \mu_0 q N_{\text{DoS}} \phi_{\text{T}}}{L} \exp \left[ \frac{C_{ox}}{C_{ox} + C_i} \left( \frac{V_{gs} - V_t}{\phi_{\text{T}}} \right) \right] \times \left[ 1 - \exp \left( \frac{-V_{ds}}{\phi_{\text{T}}} \right) \right].$$

(30)

Considering now the electrostatic potential including shortchannel effects, given by eq. (20), we have:

$$I_{ds} = \left\{ \frac{2W\mu_0 q N_{\text{DoS}} \phi_{\text{T}} \sqrt{\frac{A_2}{\pi \phi_{\text{T}}}} \exp\left(\frac{A_0}{\phi_{\text{T}}}\right)}{\operatorname{erf}\left[\sqrt{\frac{A_2}{\phi_{\text{T}}}} x_{\min}\right] + \operatorname{erf}\left[\sqrt{\frac{A_2}{\phi_{\text{T}}}} \left(L - x_{\min}\right)\right]} \right\} \times \left[1 - \exp\left(-\frac{V_{ds}}{\phi_{\text{T}}}\right)\right]. \tag{31}$$

where erf (a) is the error function, which can be approximated by [29]

$$\operatorname{erf}(a) \approx \frac{2}{\pi} \tan^{-1} \left[ \frac{\pi}{2} \left( 1.2a^4 + 0.1a^3 + 0.5a^2 + a \right) \right]$$

(32)

to obtain a fully analytical expression for the subthreshold current.

Now, taking into account the degradation of subthreshold slope due to interface traps, eq. (23), we have:

$$I_{ds} = \frac{W \mu_0 q N_{\text{DoS}} \phi_{\text{T}}}{L} \exp\left[\frac{C_{ox}}{C_{ox} + C_i + C_{it}} \left(\frac{V_{gs} - V_t}{\phi_{\text{T}}}\right)\right] \times \left[1 - \exp\left(\frac{-V_{ds}}{\phi_{\text{T}}}\right)\right]. \tag{33}$$

## C. MOBILITY DEGRADATION AND VELOCITY SATURATION

Regarding the current behavior above threshold, high values of gate or drain voltage will lead to carrier mobility degradation and velocity saturation, respectively. Both effects can be introduced semi-empirically into our compact model by modifying the parameter  $\mu(x)$ . In this case, the mobility ceases to be a fixed parameter and effectively varies with the voltages biasing the transistor.

When an intense vertical electric field is present, the charge centroid in the channel shifts towards the gate oxide or the substrate insulator, depending on the bias conditions. As a result, charge carriers become more affected by dangling bonds, interface roughness, and any fixed charges present in these dielectrics, leading to more surface scattering, which degrades the effective mobility of the two-dimensional material.

Cao et al. [12] suggest that the empirical mobility model commonly used in silicon MOSFETs can be also utilized to describe this phenomenon in 2D-FETs. Then, we have

$$\mu(x) = \frac{\mu_0}{1 + \left(\frac{\varepsilon_{ox}|E_{z_1}(x)| + \varepsilon_i|E_{z_2}(x)|}{\varepsilon_s|E_{z_C}|}\right)^{\varsigma}},$$

(34)

where  $E_{z_1}(x)$  and  $E_{z_2}(x)$  represent the vertical electric field at the interface with the oxide and in the insulator,  $E_{z_C}$  is the critical value of the vertical electric field, and  $\varsigma$  is a fitting parameter. It is important to note that  $E_{z_1}(x)$  and  $E_{z_2}(x)$  have a non-trivial dependence on V(x) through  $\varphi(x)$ , in such way that the integral in eq. (25) would need to be solved numerically.

A possible simplification to reach an analytical solution is to take a midpoint along the channel to average out an invariant value of mobility with respect to x, in such way that,  $\mu_{\text{deg}} = \mu \ (x = L/2)$ , where  $\mu \ (x)$  is calculated by eq. (34). Then,  $\mu \ (x)$  can be removed from the integral in eq. (25). To formalize an analytical expression for compact modeling of the I–V characteristics, the following definition is used:

$$\mu = \begin{cases} \mu_0, & V_{gs} \le V_t \\ \mu_{\text{deg}}, & V_{gs} > V_t \end{cases}$$

(35)

Also, when the longitudinal electric field along the channel reaches a critical value  $E_{x_C}$  at some point near the drain contact, the carrier velocity saturates, becoming equal to a constant value  $v_{sat}$ . This effect can be included in the model via a semi-empirical function widely employed to model conventional MOSFETs [14], [37]:

$$\mu(x) = \frac{\mu_0}{1 + \left[\frac{\mu_0 E_x(x)}{v_{sat}}\right]},$$

(36)

where  $E_x(x) = d\varphi(x)/dx \approx (\varphi_D - \varphi_S)/L$  within the gradual channel approximation.

As discussed in [37], besides including a field-dependent mobility term, it is also necessary to revisit the upper limit of integration in eq. (25). This is because the electrostatic potential at the drain side saturates at a value  $\varphi_{d_{val}}$ . The

**FIGURE 10.** Validation of the I–V characteristics against simulation data [12]. a)  $I_{ds} - V_{gs}$  in linear and logarithmic scales. b)  $I_{ds} - V_{ds}$  for various  $V_{gs}$  values. Parameters: monolayer MoS<sub>2</sub> channel with  $N_D = 3.5 \times 10^{11} \, \mathrm{cm}^{-2}$ , SiO<sub>2</sub> gate oxide ( $t_{ox} = 2 \, \mathrm{nm}$ ), Al<sub>2</sub>O<sub>3</sub> insulator ( $t_i = 90 \, \mathrm{nm}$ ), Al gate,  $n^{++}$  Si substrate,  $\mu_0 = 50 \, \mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1}$  and  $L = 10 \, \mathrm{m}$ .

value of the electrostatic potential for which velocity saturation occurs can be easily calculated through the condition  $dI_{ds}/d\varphi_D=0$  when  $\varphi_D=\varphi_{Dsat}$ .

With the aid of eq. (11), it is also possible to calculate the value of  $V_{ds}$  which causes current saturation:

$$V_{ds_{sat}} \cong \varphi_{D_{sat}} - \phi_{T} \ln \left[ \frac{C_{ox}}{qN_{DoS}} \left( V_{gs} - V_{t} \right) \right].$$

(37)

## **V. RESULTS AND DISCUSSION**

To demonstrate the accuracy of our expressions for the I–V characteristics, it is necessary to contrast them with simulation and experimental data available in the literature. In what follows, we seek to validate every aspect of the expressions presented in the previous sections, starting with the current-voltage relationship, obtained using our own method for the explicit calculation of the electrostatic potential.

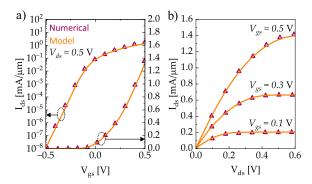

Fig. 10 shows the validation of eq. (29) against simulation data presented in [12]. The 2D-FET employs a monolayer  $MoS_2$  channel of length  $L=10\mu m$ , long enough to allow short-channel effects to be neglected. Interface traps or any other non-idealities are also not included in this particular simulation. In any case, the results provide excellent agreement and correctly reproduces the  $I_{ds}$ – $V_{gs}$  characteristics (both in linear and logarithmic scales), with a maximum relative error of 13.83% near the threshold, and  $I_{ds}$ – $V_{ds}$  for various  $V_{gs}$  values, with a maximum relative error always below 2%. The use of the analytical approximation for the electrostatic potential is demonstrated to be a very accurate description, almost identical to the exact solution obtained numerically. In this particular case, we used n=2 in eq. (13) to assure good accuracy.

Fig. 11-a shows the validation of eq. (31) against TCAD simulation (Silvaco ATLAS) data available in [13]. The device is based on a monolayer  $MoS_2$  channel with L=5.9 nm, in which short channel effects become significant. Since the device uses 2.6 nm of  $Al_2O_3$  as gate oxide, the correction concerning the effect of the lateral electric field of the oxide, eq. (21), also needs to be included. For comparison

FIGURE 11. Validation of I–V characteristics considering degradation effects in the subthreshold region. a) Short-channel effects: results from our model in contrast to TCAD simulations (Silvaco ATLAS) [13]. Parameters: Monolayer MoS $_2$  channel with  $N_D=3.5\times 10^{11}$  cm $^{-2}$ ,  $\mu_0=320~{\rm cm}^2{\rm V}^{-1}{\rm s}^{-1}$  and L=5.9 nm,  $V_{dS}=0.64$  V, HfO $_2$  gate oxide ( $t_{OX}=2.6$  nm), SiO $_2$  insulator  $t_i=270$  nm), and n $^{++}$  Si substrate. The threshold voltage was set to  $V_t=0.7$  V to match the simulation data. A factor  $\alpha=0.96\mathcal{E}_{OX}/\mathcal{E}_{SiO}_2$  was considered to account for the lateral field in the oxide. b) Interface-traps effects: results from our model in contrast to experimental data [6]. Parameters: Monolayer MoS $_2$  channel with com  $N_D=3.5\times 10^{11}~{\rm cm}^{-2}$ ,  $\mu_0=47~{\rm cm}^2{\rm V}^{-1}{\rm s}^{-1}$ ,  $L=0.5\mu{\rm m}$ ,  $W=4\mu{\rm m}$ ,  $V_{dS}=0.01$  V, HfO $_2$  gate oxide ( $t_{OX}=30~{\rm nm}$ ), SiO $_2$  insulator ( $t_i=270~{\rm nm}$ ) nm), and n $^{++}$  Si substrate. The threshold voltage set to  $V_t=0.23$  V and a trap density  $D_{it}=4\times 10^{12}~{\rm eV}^{-1}{\rm cm}^{-2}$  are employed to match the experimental data.

purposes, the subthreshold current considering a long channel (GCA approximation), eq. (30), is also presented, to illustrate the degradation of the subthreshold slope.

Fig. 11-b shows the validation of eq. (33) against experimental data presented in [6]. The MoS<sub>2</sub> layers for the experimental devices were obtained using mechanical exfoliation and transferred to a Si/SiO<sub>2</sub> substrate [6]. Next, 30 nm of HfO<sub>2</sub> were deposited using the ALD technique. Therefore, as discussed earlier, defects are expected to appear at the interfaces of the channel with adjacent layers. Here, a value of  $D_{it} = 4 \times 10^{12} \text{ eV}^{-1}\text{cm}^{-2}$  is employed to reproduce the experimental data. For comparison, the ideal subthreshold current, eq. (30) is also shown.

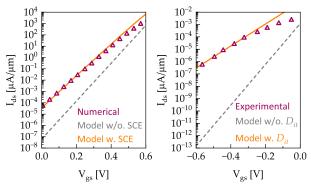

Fig. 12-a shows the validation of the current-voltage characteristics, considering now the mobility degradation, as compared to simulation data presented in [12]. The analytical approximation effectively captures the behavior of the I–V characteristics above threshold. The ideal current-characteristics, eq. (29), is also displayed for comparison. In this case,  $E_{z_C}=21\times10^7$  V/m and r=1.3 are used as fitting parameters.

Fig. 12-b shows the validation of the drain current expression, including velocity saturation, as compared to simulation data presented in [38]. The model efficiently describes the I–V characteristics in the saturation regime with  $v_{sat} = 3 \times 10^6$  cm/s, a value very close to the obtained in [38] using the Monte Carlo method. For comparison purposes, the ideal I–V curve, eq. (29), is also displayed to underscore the relevance of the correction applied to the carrier mobility, eq. (36).

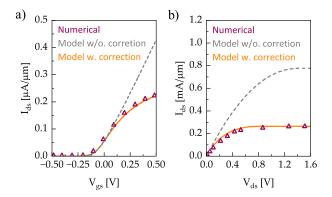

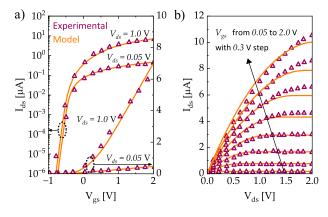

To further consolidate our work, the compact model is validated in comparison to experimental data from [39], as shown

FIGURE 12. Validation of I–V characteristics considering degradation effects above the threshold voltage. a) Mobility degradation: our results in contrast to simulation data [12]. Parameters: Monolayer MoS $_2$  channel with  $N_D=3.5\times10^{11}~{\rm cm^{-2}}$ , SiO $_2$  gate oxide  $(t_{ox}=2~{\rm nm})$ , Al $_2$ O $_3$  insulator  $(t_i=90~{\rm nm})$ , Al gate, n $^{++}$  Si substrate,  $\mu_0=50~{\rm cm^2V^{-1}\,s^{-1}}$  and  $L=10\mu$ m.  $E_{Z_C}=21\times10^7~{\rm V/m}$  and  $\varsigma=1.3$  are used as fitting parameters. b) Velocity saturation: our results in contrast to simulation data [38]. Parameters: Monolayer MoS $_2$  channel with  $N_D=3\times10^{12}~{\rm cm^{-2}}$ , HfO $_2$  gate oxide  $(t_{ox}=13~{\rm nm})$ , SiO $_2$  insulator  $(t_i=270~{\rm nm})$ , Al gate, n $^{++}$  Si substrate,  $\mu_0=50~{\rm cm^2V^{-1}\,s^{-1}}$ ,  $L=100~{\rm nm}$  and  $v_{sat}=3\times10^6~{\rm cm/s}$ .

in Fig. 13. The results demonstrate excellent agreement, correctly capturing various aspects of the I–V characteristics. A fixed fitting factor was used to match the current amplitude to the experimental data. This fitting factor represents the effect of the reported access resistance of 1.3 k $\Omega$ - $\mu$ m. On the other hand, the channel length modulation effect is not being considered, which explains the small discrepancies in the  $I_{ds}$ - $V_{ds}$  curves in saturation condition (Fig. 13-b).

FIGURE 13. Validation of I–V characteristics in comparison to experimental data [12]. a)  $I_{ds} - V_{gs}$  in linear and logarithmic scales. b)  $I_{ds} - V_{ds}$  for several  $V_{gs}$  values. Parameters: MoS<sub>2</sub> channel  $(t_s=5 \text{ nm})$  with  $N_D=5\times 10^{11} \text{ cm}^{-2}$ , ZrO<sub>2</sub> gate oxide  $(t_{ox}=20 \text{ nm})$ , SiO<sub>2</sub> insulator  $(t_j=260 \text{ nm})$ , Ni gate, n++ Si substrate,  $\mu_0=38 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ,  $L=2\mu \text{m}$  and  $W=3.3\mu \text{m}$ . A fixed fitting factor of 0.375 was used to match the current amplitude to the experimental data. This factor is related to the effect of an access resistance of 1.3 k $\Omega$ - $\mu \text{m}$  reported by the authors.

#### VI. CONCLUSION

In this paper, we have developed a compact model for 2D-FETs based on molybdenum disulfide, offering a fully

analytical, explicit, and physics-based formulation of the current-voltage characteristics. By means of a systematic approach starting from the Poisson equation and the drift-diffusion transport model, we derived closed-form expressions for the electrostatic potential, channel charge, and drain current. Key non-idealities, such as interface traps, short-channel effects, carrier mobility degradation, and velocity saturation were also incorporated into a unified analytical framework, improving the predictive capability of the model.

The proposed model is particularly well suited for integration into circuit simulation environments, given its analytical simplicity and absence of special functions or iterative procedures. These features make it a promising candidate for SPICE-compatible implementation, enabling fast and reliable circuit-level design based on 2D-FET technology. Potential applications include digital logic gates, analog front-end blocks such as amplifiers and comparators, and flexible or wearable electronics, where the use of atomic thin 2D semi-conductor channels provide key advantages.

This work focused on  $MoS_2$  due to its experimental maturity, but the modeling strategy is general and can be extended to other transition metal dichalcogenides (TMDs) or even to anisotropic 2D semiconductors such as black phosphorus, by appropriately adjusting the material parameters. Likewise, the symmetrical structure of the derived current expressions allows straightforward application to p-type devices, supporting CMOS-like design.

Looking forward, we highlight some improvements and extensions that could enhance the accuracy of the proposed model and foster its widespread adoption. For instance, the empirical mobility expression employed here, which is adapted from conventional silicon-based FET models, could be replaced by a more rigorous mobility model derived from the unique scattering mechanisms in 2D materials. This requires dedicated studies, possibly involving first-principles calculations, detailed transport simulations and experimental investigations.

Another important issue concerns the modeling of source and drain contacts. Although Schottky barrier FETs (SB-FETs) fall outside the scope of our work, contact resistance and barrier formation play a crucial role in the performance of top-gated 2D transistors. Incorporating these effects into physics-based models remains a key challenge and a necessary step towards a more complete model.

From a broader perspective, advancing compact modeling for 2D-FETs also requires bridging the gap between academic formulations and commercial-grade simulation tools. While academic models such as ours often prioritize physical insight, commercial SPICE models demand continuity, charge conservation, and numerical stability. Notable efforts, such as the S2DS model [15], have begun to address these challenges by combining physical modeling with data calibration and Verilog-A implementation. Our model contributes to this landscape by offering a more compact yet rigorous analytical formulation, which can also serve

as a basis for future developments aiming at commercial deployment.

As a final remark, the excellent electrostatic control provided by using two-dimensional materials allows a reduction of the transistor length until the ballistic limit of the current is eventually reached, as recently demonstrated for MoS<sub>2</sub> transistors [40]. In this case, carriers are able to travel through the channel without significant scattering, and the drift-diffusion (DD) formalism used in this work will be no longer valid. For this reason, we have also developed models for ballistic 2D-FETs based on the Landauer transport formalism [26], [27], [28].

In practice, the choice of drift-diffusion (DD) or Landauer ballistic transport formalisms to describe a particular device will depend on the level of maturity in each specific fabrication process. Currently, the suppression of scattering mechanisms below the level needed to assure ballistic transport is beyond the reach of most research groups, in such way that DD-based models will stay strongly relevant in the near to mid future and even in the long term, for quite a few of the more challenging materials.

#### **REFERENCES**

- P. R. Wallace, "The band theory of graphite," *Phys. Rev.*, vol. 71, no. 9, pp. 622–634, May 1947, doi: 10.1103/physrev.71.622.

- [2] H. P. Boehm, A. Clauss, G. Fischer, and U. Hofmann, "Surface properties of extremely thin graphite lamellae," in *Proc. 5th Conf. Carbon*. Amsterdam, The Netherlands: Elsevier, 1962, pp. 73–80, doi: 10.1016/b978-0-08-009707-7.50013-3.

- [3] K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, "Electric field effect in atomically thin carbon films," *Science*, vol. 306, no. 5696, pp. 666–669, Oct. 2004, doi: 10.1126/science.1102896.

- [4] S. V. Morozov, K. S. Novoselov, M. I. Katsnelson, F. Schedin, D. C. Elias, J. A. Jaszczak, and A. K. Geim, "Giant intrinsic carrier mobilities in graphene and its bilayer," *Phys. Rev. Lett.*, vol. 100, no. 1, Jan. 2008, Art. no. 016602, doi: 10.1103/physrevlett.100.016602.

- [5] P. Miró, M. Audiffred, and T. Heine, "An atlas of two-dimensional materials," *Chem. Soc. Rev.*, vol. 43, no. 18, pp. 6537–6554, 2014, doi: 10.1039/c4cs00102h.

- [6] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer MoS<sub>2</sub> transistors," *Nature Nanotechnol.*, vol. 6, no. 3, pp. 147–150, Mar. 2011, doi: 10.1038/nnano.2010.279.

- [7] X. Yang, J. Li, R. Song, B. Zhao, J. Tang, L. Kong, H. Huang, Z. Zhang, L. Liao, Y. Liu, X. Duan, and X. Duan, "Highly reproducible van der Waals integration of two-dimensional electronics on the wafer scale," *Nature Nanotechnol.*, vol. 18, no. 5, pp. 471–478, Mar. 2023, doi: 10.1038/s41565-023-01342-1.

- [8] K. Zhu, C. Wen, A. A. Aljarb, F. Xue, X. Xu, V. Tung, X. Zhang, H. N. Alshareef, and M. Lanza, "The development of integrated circuits based on two-dimensional materials," *Nature Electron.*, vol. 4, no. 11, pp. 775–785, Nov. 2021, doi: 10.1038/s41928-021-00672-z.

- [9] Y. Liu, X. Duan, H.-J. Shin, S. Park, Y. Huang, and X. Duan, "Promises and prospects of two-dimensional transistors," *Nature*, vol. 591, no. 7848, pp. 43–53, Mar. 2021, doi: 10.1038/s41586-021-03339-z.

- [10] M. C. Lemme, D. Akinwande, C. Huyghebaert, and C. Stampfer, "2D materials for future heterogeneous electronics," *Nature Commun.*, vol. 13, no. 1, p. 1392, Mar. 2022, doi: 10.1038/s41467-022-29001-4.

- [11] D. Jiménez, "Drift-diffusion model for single layer transition metal dichalcogenide field-effect transistors," *Appl. Phys. Lett.*, vol. 101, no. 24, pp. 8–11, Dec. 2012, doi: 10.1063/1.4770313.

- [12] W. Cao, J. Kang, W. Liu, and K. Banerjee, "A compact current–voltage model for 2D semiconductor based field-effect transistors considering interface traps, mobility degradation, and inefficient doping effect," *IEEE Trans. Electron Devices*, vol. 61, no. 12, pp. 4282–4290, Dec. 2014, doi: 10.1109/TED.2014.2365028.

- [13] W.-X. You and P. Su, "A compact subthreshold model for short-channel monolayer transition metal dichalcogenide field-effect transistors," *IEEE Trans. Electron Devices*, vol. 63, no. 7, pp. 2971–2974, Jul. 2016, doi: 10.1109/TED.2016.2564424.

- [14] Y. Taur, J. Wu, and J. Min, "A short-channel *I–V* model for 2-D MOS-FETs," *IEEE Trans. Electron Devices*, vol. 63, no. 6, pp. 2550–2555, Jun. 2016, doi: 10.1109/TED.2016.2547949.

- [15] S. V. Suryavanshi and E. Pop, "S<sub>2</sub>DS: Physics-based compact model for circuit simulation of two-dimensional semiconductor devices including non-idealities," *J. Appl. Phys.*, vol. 120, no. 22, Dec. 2016, Art. no. 224503, doi: 10.1063/1.4971404.

- [16] C. Yadav, A. Agarwal, and Y. S. Chauhan, "Compact modeling of transition metal dichalcogenide based thin body transistors and circuit validation," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 1261–1268, Mar. 2017, doi: 10.1109/TED.2016.2643698.

- [17] L. F. Deng, C. M. Si, H. Q. Huang, J. Wang, H. Wen, and S. Im, "Explicit continuous I–V model for 2D transition metal dichalcogenide field-effect transistors," *Microelectron. J.*, vol. 88, pp. 61–66, Jun. 2019, doi: 10.1016/j.mejo.2019.04.008.

- [18] K. S. Novoselov, D. Jiang, F. Schedin, T. J. Booth, V. V. Khotkevich, S. V. Morozov, and A. K. Geim, "Two-dimensional atomic crystals," *Proc. Nat. Acad. Sci. USA*, vol. 102, no. 30, pp. 10451–10453, Jul. 2005, doi: 10.1073/pnas.0502848102.

- [19] A. Splendiani, L. Sun, Y. Zhang, T. Li, J. Kim, C.-Y. Chim, G. Galli, and F. Wang, "Emerging photoluminescence in monolayer MoS<sub>2</sub>," *Nano Lett.*, vol. 10, no. 4, pp. 1271–1275, Apr. 2010, doi: 10.1021/nl903868w.

- [20] U. K. Sahu, A. Kumar Saha, P. S. Gupta, and H. Rahaman, "Valley resolved current components analysis of monolayer TMDFETs," in *Proc. Int. Symp. Devices, Circuits Syst. (ISDCS)*, Mar. 2020, pp. 1–5, doi: 10.1109/ISDCS49393.2020.9263002.

- [21] S. Haastrup, M. Strange, M. Pandey, T. Deilmann, P. S. Schmidt, N. F. Hinsche, M. N. Gjerding, D. Torelli, P. M. Larsen, A. C. Riis-Jensen, J. Gath, K. W. Jacobsen, J. Jørgen Mortensen, T. Olsen, and K. S. Thygesen, "The computational 2D materials database: High-throughput modeling and discovery of atomically thin crystals," 2D Mater., vol. 5, no. 4, Sep. 2018, Art. no. 042002, doi: 10.1088/2053-1583/aacfc1.

- [22] M. N. Gjerding, A. Taghizadeh, A. Rasmussen, S. Ali, F. Bertoldo, T. Deilmann, N. R. Knøsgaard, M. Kruse, A. H. Larsen, S. Manti, T. G. Pedersen, U. Petralanda, T. Skovhus, M. K. Svendsen, J. J. Mortensen, T. Olsen, and K. S. Thygesen, "Recent progress of the computational 2D materials database (C2DB)," 2D Mater., vol. 8, no. 4, Oct. 2021, Art. no. 044002, doi: 10.1088/2053-1583/ac1059.

- [23] Y. Park, N. Li, D. Jung, L. T. Singh, J. Baik, E. Lee, D. Oh, Y. D. Kim, J. Y. Lee, J. Woo, S. Park, H. Kim, G. Lee, G. Lee, and C.-C. Hwang, "Unveiling the origin of n-type doping of natural MoS<sub>2</sub>: Carbon," npj 2D Mater. Appl., vol. 7, no. 1, p. 60, Sep. 2023, doi: 10.1038/s41699-023-00424-x.

- [24] N. Fang and K. Nagashio, "Accumulation-mode two-dimensional field-effect transistor: Operation mechanism and thickness scaling rule," ACS Appl. Mater. Interface, vol. 10, no. 38, pp. 32355–32364, Sep. 2018, doi: 10.1021/acsami.8b10687.

- [25] A. M. de Souza, D. R. Celino, R. Ragi, and M. A. Romero, "Fully analytical compact model for the Q–V and C–V characteristics of cylindrical junctionless nanowire FETs," *Microelectron. J.*, vol. 119, Jan. 2022, Art. no. 105324, doi: 10.1016/j.mejo.2021.105324.

- [26] A. M. de Souza, D. R. Celino, and M. A. Romero, "Compact modeling of transition metal dichalcogenide ballistic transistors," in *Proc. 37th Symp. Microelectron. Technol. Devices (SBMicro)*, Aug. 2023, pp. 1–4, doi: 10.1109/sbmicro60499.2023.10302479.

- [27] A. M. de Souza, D. R. Celino, and M. A. Romero, "Analytical model for monolayer phosphorene DG-FETs in the ballistic regime," in *Proc. IEEE Nanotechnol. Mater. Devices Conf. (NMDC)*, Oct. 2023, pp. 811–814.

- [28] A. M. de Souza, D. R. Celino, R. Ragi, and M. A. Romero, "A physics-based analytical model for ballistic InSe nanotransistors," in *Proc. IEEE 24th Int. Conf. Nanotechnol. (NANO)*, Spain, Jul. 2024, pp. 185–190, doi: 10.1109/NANO61778.2024.10628708.

- [29] X. Liang, Analytical Modeling of Short Channel Effects in Double Gate MOSFET, vol. Universidade Califórnia, 2006.

- [30] N. Fang, S. Toyoda, T. Taniguchi, K. Watanabe, and K. Nagashio, "Full energy spectra of interface state densities for n- and p-type MoS<sub>2</sub> fieldeffect transistors," *Adv. Funct. Mater.*, vol. 29, no. 49, pp. 1–9, Dec. 2019, doi: 10.1002/adfm.201904465.

- [31] H. Qiu, T. Xu, Z. Wang, W. Ren, H. Nan, Z. Ni, Q. Chen, S. Yuan, F. Miao, F. Song, G. Long, Y. Shi, L. Sun, J. Wang, and X. Wang, "Hopping transport through defect-induced localized states in molybdenum disulphide," *Nature Commun.*, vol. 4, no. 1, p. 2642, Oct. 2013, doi: 10.1038/ncomms3642.

- [32] P. Zhao, A. Khosravi, A. Azcatl, P. Bolshakov, G. Mirabelli, E. Caruso, C. L. Hinkle, P. K. Hurley, R. M. Wallace, and C. D. Young, "Evaluation of border traps and interface traps in HfO<sub>2</sub>/MoS<sub>2</sub> gate stacks by capacitance–voltage analysis," 2D Mater., vol. 5, no. 3, Apr. 2018, Art. no. 031002, doi: 10.1088/2053-1583/aab728.

- [33] N. Fang and K. Nagashio, "Band tail interface states and quantum capacitance in a monolayer molybdenum disulfide field-effect-transistor," *J. Phys. D, Appl. Phys.*, vol. 51, no. 6, Feb. 2018, Art. no. 065110, doi: 10.1088/1361-6463/aaa58c.

- [34] W. Li, "Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices," *Nature Electron.*, vol. 2, no. 12, pp. 563–571, Dec. 2019, doi: 10.1038/s41928-019-0334-y.

- [35] Y. Xu, W. S. Li, D. Fan, Y. Shi, H. Qiu, and X. Wang, "A compact model for transition metal dichalcogenide field effect transistors with effects of interface traps," in *Proc. 5th IEEE Electron Devices Tech*nol. Manuf. Conf. (EDTM), Apr. 2021, pp. 1–3, doi: 10.1109/edtm50988. 2021 9420973

- [36] S. Luryi, "Quantum capacitance devices," Appl. Phys. Lett., vol. 52, no. 6, pp. 501–503, Feb. 1988, doi: 10.1063/1.99649.

- [37] J. Cao, W. Liu, Q. Wu, G. Yang, N. Lu, Z. Ji, D. Geng, L. Li, and M. Liu, "A new velocity saturation model of MoS<sub>2</sub> field-effect transistors," *IEEE Electron Device Lett.*, vol. 39, no. 6, pp. 893–896, Jun. 2018, doi: 10.1109/LED.2018.2830400.

- [38] A. Pilotto, P. Khakbaz, P. Palestri, and D. Esseni, "Semi-classical transport in MoS<sub>2</sub> and MoS<sub>2</sub> transistors by a Monte Carlo approach," *Solid-State Electron.*, vol. 192, Jun. 2022, Art. no. 108295, doi: 10.1016/j.sse.2022.108295.

- [39] A. B. Sachid, M. Tosun, S. B. Desai, C.-Y. Hsu, D.-H. Lien, S. R. Madhvapathy, Y.-Z. Chen, M. Hettick, J. S. Kang, Y. Zeng, J.-H. He, E. Y. Chang, Y.-L. Chueh, A. Javey, and C. Hu, "Monolithic 3D CMOS using layered semiconductors," *Adv. Mater.*, vol. 28, no. 13, pp. 2547–2554, Apr. 2016, doi: 10.1002/adma.201505113.

- [40] J. Jiang, L. Xu, L. Du, L. Li, G. Zhang, C. Qiu, and L.-M. Peng, "Yttrium-doping-induced metallization of molybdenum disulfide for ohmic contacts in two-dimensional transistors," *Nature Electron.*, vol. 7, no. 7, pp. 545–556, May 2024, doi: 10.1038/s41928-024-01176-2.

**ADELCIO M. DE SOUZA** received the B.Sc. degree in telecommunications engineering from the National Institute of Telecommunications (Inatel), Santa Rita do Sapucaí, Brazil, in 2016, and the M.Sc. and Ph.D. degrees in electrical engineering from the University of São Paulo (USP), São Carlos, Brazil, in 2018 and 2024, respectively.

His major fields of study include optical communications, semiconductor devices, and integrated photonics. He is currently a Postdoctoral

Researcher with USP, where he works on designing, fabricating, and characterizing photonic integrated circuits for high-speed optical fronthaul in 6G communication systems. His doctoral research contributed to the understanding and modeling of transistors based on junctionless nanowires and two-dimensional materials. He has authored/co-authored several papers in journals and conferences and participated in collaborative projects funded by Brazilian agencies FAPESP, CAPES, and CNPq.

**DANIEL R. CELINO** received the B.Sc. degree in electrical engineering from the Federal University of Espírito Santo (UFES), Vitória, Brazil, in 2012, and the M.Sc. and Ph.D. degrees in electrical engineering from the University of São Paulo (USP), São Carlos, Brazil, in 2017 and 2024, respectively.

His major fields of study include optical communications, semiconductor devices, and integrated circuits. He is currently a Lead Application Engineer at Cadence Design Systems,

Belo Horizonte, Brazil, where he works on all phases of IC design projects. His doctoral research contributed to the understanding and modeling of resonant tunneling diodes. He has authored/co-authored several papers in journals and conferences and participated in collaborative projects funded by Brazilian agencies FAPESP, CAPES, and CNPq.

**REGIANE RAGI** received the B.Sc., M.Sc., and Ph.D. degrees from the Physics Institute of the University of São Paulo (IF-USP), São Paulo, Brazil, in 1994, 1997, and 2003, respectively.

She has held academic positions at the USP and the Federal University of São Carlos (UFSCar), Brazil. She authored the undergraduate textbook computational physics for engineering and physics and several other teaching materials available through the Livraria da Física publishing company.

Some of these more recent publications are dedicated to spread the use of SAAM, a technique she developed to obtain approximated analytical of transcendental equations and related problems. She also maintains a blog and a video-channel, focusing on scientific programming for young scientists and engineers. Her research interests include solid-state and nanoelectronic devices.

MURILO A. ROMERO (Senior Member, IEEE) was born in Rio de Janeiro, Brazil, in 1965. He received the B.Sc. and M.Sc. degrees from the Catholic University of Rio de Janeiro, Rio de Janeiro, in 1988 and 1991, respectively, and the Ph.D. degree from Drexel University, Philadelphia, PA, USA, in 1995.

After his return to Brazil in 1995, he joined the University of São Paulo (USP), São Carlos, as a Faculty Member. At USP, he became an Associate

Professor in 2001 and a Full Professor in 2008. He was then the Head of the Electrical Engineering Department, EESC, USP, from 2009 to 2013, and the Chair of the Electrical and Biomedical Engineering Committee of Brazilian Research Council (CNPq), from 2011 to 2013, and the Head of the Electrical Engineering area at CAPES, from 2014 to 2017, an accreditation agency of Brazilian Government, established to carry out quality assurance of graduate studies in Brazil, both at the master's and doctoral levels. His research interests span over a large variety of topics in electrical engineering. He holds two patents and has published about 200 journal and conference papers, including manuscripts at IEEE Transactions on MICROWAVE THEORY AND TECHNIQUES, IEEE JOURNAL OF QUANTUM ELECTRONICS, IEEE PHOTONICS TECHNOLOGY LETTERS, IEEE TRANSACTIONS ON CIRCUITS AND Systems—I: Regular Papers, IEEE Transactions on Electron Devices, IEEE TRANSACTIONS ON NANOTECHNOLOGY, IEEE/OSA JOURNAL OF LIGHTWAVE TECHNOLOGY, IEEE SENSORS JOURNAL, IEEE ACCESS, and IEEE TRANSACTIONS ON INFORMATION FORENSICS AND SECURITY, among other top-ranked iournals

. . .

Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES) - ROR identifier: 00x0ma614