**Boletim Técnico da Escola Politécnica da USP**

**Departamento de Engenharia de Computação e**

**Sistemas Digitais**

ISSN 1413-215X

**BT/PCS/0219**

---

**Avaliação de Performance de

Arquiteturas para Computação

de Alto Desempenho**

---

**Karin Strauss

Wilson Vicente Ruggiero**

3208833

~~#298213~~

**São Paulo - 2002**

O presente trabalho é um resumo da dissertação de mestrado apresentada por Karin Strauss, sob orientação do Prof. Dr. Wilson V. Ruggiero: "Avaliação de Performance de Arquiteturas para Computação de Alto Desempenho", defendida em 09/08/2002, na EPUSP.

A íntegra da dissertação encontra-se à disposição com o autor e na biblioteca de Engenharia de Eletricidade da Escola Politécnica da USP.

#### FICHA CATALOGRÁFICA

Strauss, Karin

Avaliação de performance de arquiteturas para computação de alto desempenho / K. Strauss, W.V. Ruggiero. – São Paulo : EPUSP, 2002.

12 p. – (Boletim Técnico da Escola Politécnica da USP, Departamento de Engenharia de Computação e Sistemas Digitais, BT/PCS/0219)

1. Arquitetura e organização de computadores 2. ATM (Redes de computadores) 3. Simulação de sistemas I. Ruggiero, Wilson Vicente II. Universidade de São Paulo. Escola Politécnica. Departamento de Engenharia de Computação e Sistemas Digitais III. Título IV. Série ISSN 1413-215X

CDD 004.22

004.6

003.3

# Avaliação de Performance de Arquiteturas para Computação de Alto Desempenho

julho de 2002

## Resumo

Este trabalho apresenta a avaliação de desempenho de três componentes de arquitetura inovadora criados no Projeto Blue Gene, da IBM. Com a crescente demanda por poder computacional e a incapacidade de computadores baseados no modelo seqüencial em atender essa demanda, surgiram os computadores paralelos. Uma arquitetura surgida dessa evolução é conhecida como arquitetura celular. Ela baseia-se na simplicidade dos elementos de computação e no vasto paralelismo, sendo que o trabalho conjunto de muitas células resulta em grandes computações. Esse campo, porém, é relativamente novo e pouco explorado. Um dos projetos que pretendem estudar e construir máquinas de arquitetura celular é o Projeto Blue Gene, sendo desenvolvido no IBM T.J.Watson Research Center. Além da inovação na arquitetura da máquina como um todo, também foram propostas inovações específicas como a arquitetura dos próprios processadores, unidades de ponto flutuante e redes de interconexão. Foram escolhidos três dos componentes de arquitetura mais inovadora para o estudo, com o objetivo de avaliar sua capacidade antes mesmo de sua fabricação. Assim, é possível, se necessário, alterar o projeto dos componentes sem grande impacto no orçamento, já que os custos de refazer o processo de fabricação são evitados.

### **Abstract**

In this work, we present a performance analysis of three key architectural features of the IBM Blue Gene Project. The demand for computational power continues to increase at a fast rate. Computers based on the sequential processing model can no longer meet the performance expectations imposed by the market. Therefore, parallel computers have been used to address this demand. One of the approaches resulting from this evolution into massively parallel systems is known as "cellular computing". Its basic principles are simplicity and vast parallelism. One of the current research projects that are studying and building cellular architecture machines is the Blue Gene Project, at the IBM T.J.Watson Research Center. This project is innovative both from a system architecture perspective and from the perspective of specific technologies being used. New architectural solutions are being developed for the processors, the floating point units, and the interconnection networks. Our goal is to evaluate the behavior of three of the most innovative architectural components of Blue Gene, primarily from a performance perspective, before the machine is actually built. It is then possible to change the design of those components in response to the evaluation results without requiring another fabrication iteration.

1 Introdução

Poder computacional é cada vez mais necessário nos dias de hoje, tanto em aplicações comerciais quanto em aplicações científicas. Por isso, as grandes empresas de computação têm investido muito esforço no desenvolvimento de supercomputadores de grande poder computacional e de altíssimo desempenho. Projetos ambiciosos têm surgido a partir dos investimentos destas empresas, alguns até pretendendo produzir máquinas com poder maior do que o dos 500 maiores supercomputadores atuais somados.

Um desses projetos surgiu no centro de pesquisas T.J.Watson, da IBM. Trata-se do projeto Blue Gene [2] [6] [3], que visa desenvolver uma série de supercomputadores de arquitetura inovadora. O projeto baseia-se na idéia de se construir máquinas paralelas em forma celular, ou seja, compostas de blocos simples e de mesma estrutura (células), ligados apenas a alguns outros blocos vizinhos semelhantes [10]. Através da ligação desses blocos seria possível construir uma máquina paralela de alto desempenho e grande escalabilidade, já que, caso se necessite de mais poder computacional, basta adicionar mais células.

Além da inovação do ponto de vista de ligação entre os componentes do sistema paralelo e das redes de interconexão, pretende-se, no projeto Blue Gene, inovar em aspectos arquiteturais mais específicos, como na arquitetura do próprio processador e de unidades auxiliares.

Avaliar o sistema como um todo, de uma só vez, é uma tarefa bastante complicada: por isso, divide-se a avaliação em tarefas menores, que enfocam subsistemas mais restritos, tornando a análise mais simples.

Os primeiros subsistemas a passar por avaliação são, normalmente, os de arquitetura mais inovadora, justamente porque seu comportamento ainda não é dominado pelos projetistas. Em seguida, passa-se a fazer avaliações mais abrangentes, examinando a interação entre os diversos componentes do sistema.

Avaliar e validar o ganho de desempenho com certos aspectos arquiteturais do sistema é de grande importância para o sucesso do projeto e, para que isso seja possível antes mesmo de a máquina real existir, são usados simuladores [5] [8].

Num projeto de grande porte como o Blue Gene, há vários grupos de pessoas distintos envolvidos. Cada um desses grupos está interessado em aspectos diferentes das máquinas. Assim, simuladores distintos são utilizados para a obtenção de dados em níveis de detalhes variados.

Pode-se, também, obter resultados dos simuladores mais detalhados e mais lentos para calibrar os simuladores mais rápidos e menos detalhados. Dessa forma, aumenta-se a precisão desses últimos, tornando possível estimar o desempenho do sistema com *workloads* reais em tempos razoavelmente pequenos.

As avaliações de desempenho em um projeto como esse são numerosas e freqüentemente utilizam-se de um ou mais simuladores, com diferentes níveis de detalhes.

O objetivo principal da pesquisa foi avaliar o desempenho de três componentes diferentes das máquinas em desenvolvimento no projeto Blue Gene.

Os três componentes estudados foram cuidadosamente escolhidos por serem três fatores significativos para a estimativa do desempenho geral dos supercomputadores Blue Gene. Analisar o impacto de cada um dos componentes no desempenho do sistema, e os custos associados a eles, em momento prévio à fabricação das máquinas é importante pois, nessa fase, ainda é possível fazer alterações no projeto.

O primeiro componente é o processador Cyclops. Esse processador é composto por um número grande de unidades de execução, também chamadas de *threads*. Essas unidades de execução compartilham memória *cache*, memória principal e unidades de ponto flutuante. A forma como as *threads* compartilham o *cache* de dados é configurável através da forma de endereçamento.

O Cyclops tem uma arquitetura bastante inovadora, cujo comportamento ainda não é completamente conhecido e dominado. Além disso, é uma das opções de processador que podem ser empregados em supercomputadores Blue Gene. Algumas das grandes preocupações dos projetistas são qual banda de memória pode ser obtida com a utilização do *chip*, se é possível atingir o limite teórico calculado e quais políticas devem ser usadas para que isso aconteça. Assim, a avaliação de desempenho da banda de memória do *chip* é um tópico relevante de pesquisa, que pode ajudar os projetistas a estimar o desempenho geral de uma máquina construída com blocos básicos desse tipo.

O objetivo é, então, estudar o comportamento da taxa de transferência de dados entre as *threads* e a memória principal e verificar se é possível atingir o limite teórico calculado, com várias configurações de *cache* de dados e de distribuição de dados na memória principal.

O segundo componente é uma unidade de ponto flutuante dupla. Essa é uma unidade denominada

pela própria IBM como SIMOMD (*Single Instruction, Multiple Operation, Multiple Data*), por ter instruções paralelas, cruzadas, assimétricas e complexas.

A unidade de ponto flutuante dupla também é um projeto bastante novo e pouco explorado. Sua arquitetura apresenta diferenças relevantes em relação a outras unidades de ponto flutuante paralelas, já que possibilita não só operações paralelas como também operações cruzadas, assimétricas e complexas. Isso facilita muitas operações freqüentemente utilizadas em aplicações científicas, incluindo diversas computações de álgebra linear (multiplicação de matrizes, por exemplo) e com números complexos. Para que seja possível aproveitar todo o potencial que a unidade pode oferecer, é necessário que haja suporte de compiladores, e que as aplicações sejam codificadas de forma adequada. Assim, a avaliação é feita sobre o conjunto arquitetura-compilador-aplicação. Como o projeto Blue Gene é bastante voltado à construção de máquinas de alto desempenho para aplicações científicas, e esse componente tem bastante influência no desempenho geral, é importante ter dados a seu respeito.

O objetivo é, então, estudar os ganhos de se ter uma unidade de ponto flutuante dupla como esta em relação a uma unidade simples similar. Nesse caso, a avaliação de desempenho não se restringe apenas à arquitetura. Devem ser também levados em conta o compilador e os algoritmos utilizados.

O terceiro componente é a forma de interconexão entre as células do sistema. Essas células farão sua comunicação através de várias redes distintas. A rede a ser estudada apresenta uma topologia toroidal e constitui a principal rede para aplicações do Blue Gene.

A arquitetura altamente paralela da máquina a ser construída implica em uma comunicação entre células muito intensa, já que a computação e os dados estão distribuídos entre eles. Esse comportamento de comunicação pode influenciar negativamente o desempenho da computação. Assim, o desempenho da rede de interconexão é, novamente, um fator importante para o desempenho geral da máquina, e deve ser estudado.

O objetivo é, então, avaliar o desempenho de um algoritmo distribuído bastante utilizado em computação científica, verificando a eficácia dessa rede de interconexão.

As demais seções deste artigo estão organizadas da seguinte forma: na seção 2 é apresentada a avaliação de desempenho do processador Cyclops; na seção 3 a avaliação de desempenho da unidade de ponto flutuante dupla é explicada; a seção 4 mostra a avaliação de desempenho da rede de interconexão toroidal estudada; na seção 5 são apresentadas as conclusões e comentados os trabalhos futuros.

## 2 Cyclops

O *Cyclops* é uma unidade básica que pode ser utilizada na construção de uma das máquinas Blue Gene. Trata-se de uma célula *SMP* (*Symmetric Multi-Processor*) com múltiplas linhas de execução (daqui em diante chamadas de *threads*), memória embutida e dispositivos de comunicação integrados.

O *Cyclops* é ainda uma arquitetura em desenvolvimento. A configuração do *chip* estudada neste trabalho será descrita a seguir.

O *chip* consiste em 128 *threads* com 64 registradores de 32 bits cada. Cada registrador tem precisão simples (32 bits), mas é possível agrupar dois registradores em um par para prover precisão dupla (64 bits). Além disso, cada *thread* tem um contador de instruções (*PC*) e uma unidade lógico-aritmética de ponto fixo.

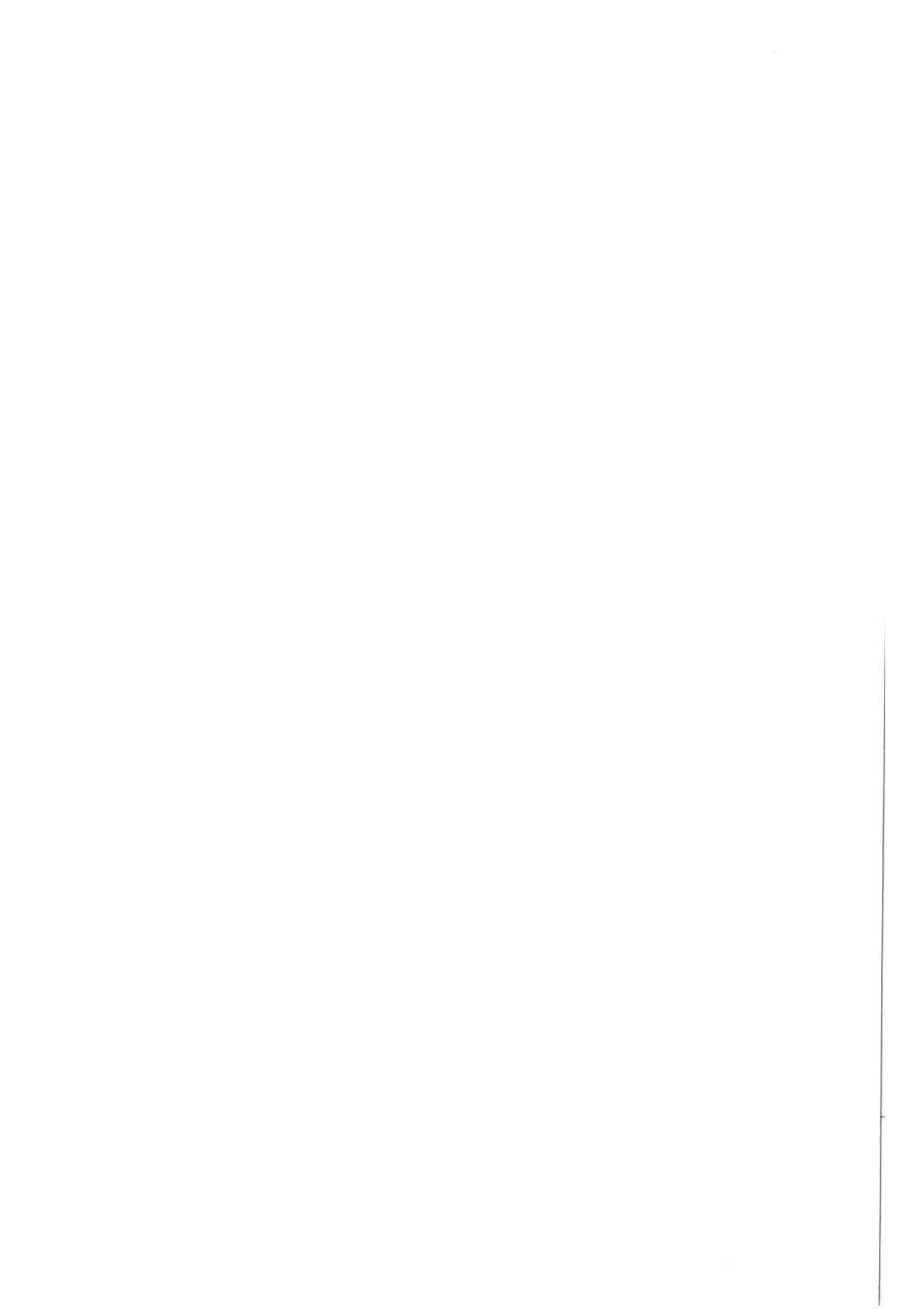

Essas *threads* são organizadas em grupos de 4, chamados de *quads*. Cada *quad*, portanto, consiste nessas 4 *threads* que compartilham uma unidade de ponto flutuante e uma unidade de *cache* de dados de 16 KB. Cada dois *quads* compartilham um *cache* de instruções de 32 KB, de associatividade 8-way e linha de 64 bytes. A memória principal, compartilhada por todas as *threads*, consiste em 8 MB, divididos em 16 bancos de 512 KB. O *chip* inclui, também, hardware de interconexão (A-switch e B-switch) e um controlador para acessar memória externa (opcional). Essa configuração pode ser observada na figura 1.

Se duas ou mais *threads* tentam utilizar o mesmo recurso em um mesmo ciclo, uma delas é

Figura 1: Diagrama de blocos do chip analisado (Cyclops)

selecionada como a vencedora e aloca o recurso. As *threads* restantes esperam até que o recurso esteja disponível. A decisão de qual *thread* tem prioridade é feita utilizando-se a técnica de *round-robin*, para garantir que todas as *threads* terão a mesma chance de utilização de um recurso.

O *chip* Cyclops ainda possui um mecanismo de sincronização entre *threads* por *hardware*. Esse mecanismo permite que se faça sincronizações muito rápidas, da ordem de alguns ciclos após a última *thread* chegar à barreira.

Como já explicado, a memória principal do *chip* consiste em 16 bancos de 512 KB, num total de 8 MB. São utilizados apenas 24 bits para o endereçamento físico da memória. Os 8 bits restantes são utilizados para definir no *cache* de qual *quad* os dados serão colocados. Os dados podem ser colocados em um *cache* pertencente ao mesmo *quad* da *thread* que os requisitaram ou em outro *cache* definido por esses 8 bits.

Como os dados podem ser colocados em qualquer um dos *caches*, dependendo do *software*, aparece um problema de consistência de dados. Esse problema só pode ser evitado com uma programação cuidadosa, já que não há suporte de *hardware* para isso.

O tempo de acesso em modo *burst* para dois blocos de 32 bytes subseqüentes em um banco de memória, ou seja, 64 bytes, é de 12 ciclos. Pode-se fazer acessos simultâneos a todos os bancos de memória. Assim, supondo uma freqüência de excitação de 500 MHz, temos uma banda teórica de 42GB/s ( $64\text{ B} \times 16\text{ bancos} \times 500\text{ MHz} / 12\text{ ciclos}$ ).

Para o estudo, foi utilizado o STREAM *benchmark* [7][13] executado sobre um simulador de instruções específico para o *chip*, que inclui o modelo de *threads* e compartilhamento de recursos e é capaz de fornecer estimativas de tempo. O STREAM foi desenvolvido especialmente para a medição de banda de memória e consiste em quatro operações com vetores: cópia (Copy), adição (Add), multiplicação por escalar (Scale) e multiplicação-e-soma (Triad).

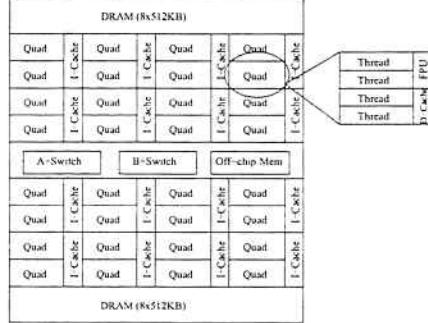

Os experimentos indicaram que é possível atingir a banda máxima teórica quando se traz os dados para o *cache* pertencente ao mesmo *quad* da *thread* que os acessaram. Pode-se comparar o desempenho do *chip* com o de uma máquina comercial, como mostra a figura 2.

Pode-se notar que os vetores usados com o SGI Origin 3800/400 são muito maiores, e que o Cyclops não tem memória suficiente para experimentos com vetores deste tamanho.

De qualquer forma, é importante notar que um único chip do Cyclops pode atingir banda de memória sustentável comparável à atingida por uma máquina comercial topo-de-linha.

Figura 2: Comparação da performance de (a) Cyclops (tamanho do vetor: 249.984 elementos) *vs.* performance de (b) SGI Origin 3800-400 (tamanho do vetor: 5.000.000 elementos por processador)

### 3 Unidade de Ponto Flutuante Dupla

A unidade de ponto flutuante dupla estudada, chamada *PowerPC 440 FP2* é uma extensão da unidade de ponto flutuante simples projetada para o processador *PowerPC 440*, chamada *PowerPC 440 FPU*. Ela será utilizada em uma das máquinas Blue Gene.

A arquitetura projetada baseia-se na duplicação da unidade original. Uma das unidades é, então, chamada de primária e a outra é chamada de secundária. As instruções originais, ou seja, as instruções normais da unidade de ponto flutuante simples, destinam-se à unidade primária. Foram adicionadas novas instruções ao *instruction-set*, tanto para operações simultâneas nas duas unidades quanto para operações na unidade secundária, estas similares às instruções primárias. Cada uma das unidades tem seu próprio banco de registradores, que podem ser endereçados separadamente. Também é possível endereçar os dois registradores de uma só vez. Pode-se, ainda, mover dados entre os bancos de registradores.

As novas instruções com as duas unidades incluem operações paralelas, cruzadas, assimétricas e complexas. A tabela 3 mostra alguns exemplos. As instruções assimétricas realizam operações diferentes mas relacionadas, nos dois caminhos de dados, enquanto que as instruções complexas podem ser simétricas ou assimétricas, mas são especificamente voltadas para computações com números complexos. O nome dado ao tipo de operações que a unidade é capaz de executar é SIMOMD, ou seja, *Single Instruction Multiple Operation Multiple Data*.

| Classe      | Exemplo                 | Operação na<br>Unid. Primária | Operação na<br>Unid. Secundária |

|-------------|-------------------------|-------------------------------|---------------------------------|

| Paralela    | fpmadd fT, fA, fB, fC   | $P_T = P_A * P_C + P_B$       | $S_T = S_A * S_C + S_B$         |

| Cruzada     | fxcpmadd fT, fA, fB, fC | $P_T = P_A * P_C + P_B$       | $S_T = P_A * S_C + S_B$         |

|             | fxmadd fT, fA, fB, fC   | $P_T = P_A * S_C + P_B$       | $S_T = S_A * P_C + S_B$         |

| Assimétrica | fxcpnpma fT, fA, fB, fC | $P_T = -P_A * P_C + P_B$      | $S_T = P_A * S_C + S_B$         |

| Complexa    | fxcxnpma fT, fA, fB, fC | $P_T = -S_A * S_C + P_B$      | $S_T = S_A * P_C + S_B$         |

Tabela 1: Exemplo de instruções da *PowerPC 440 FP2*

É possível, com essa unidade, fazer transferências de dados de palavras de 128 *bits*. Uma palavra de 64 *bits* é colocada no registrador primário selecionado na instrução e a outra é colocada no registrador secundário correspondente. Nesse caso, os registradores são encarados como pares. Se um dado é colocado no terceiro registrador primário, o dado subsequente será colocado no terceiro registrador secundário. O equivalente pode acontecer se a operação for um *store*.

As operações de movimentação de dados podem ser paralelas, onde a palavra endereçada na instrução é colocada em um registrador primário, também selecionado na instrução, e a palavra consecutiva a ela é colocada no registrador secundário correspondente.

Outro modo de movimentação de dados é a operação cruzada. Nesse caso, a palavra endereçada é colocada em um registrador secundário selecionado na instrução e a palavra seguinte é colocada no registrador primário.

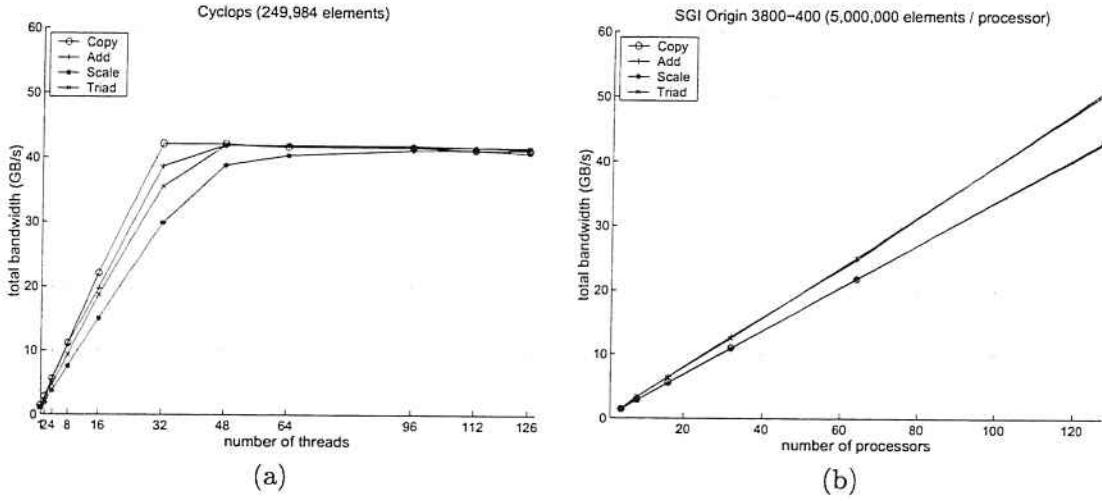

Para que esse tipo de operação seja eficiente, porém, os dados devem estar alinhados em relação a seu tamanho (dados de 32 *bits* alinhados em posições com endereço múltiplo de 4 *bytes*, dados de 64 *bits* alinhados em endereço múltiplo de 8 *bytes*) e precisa se encaixar completamente em uma região alinhada de 256 *bits*, ou 32 *bytes*, que é o tamanho de uma linha do *cache* do PowerPC 440. Além disso, uma transferência não pode cruzar o meio de uma linha de cache. As transferências válidas estão ilustradas na figura 3.

As restrições podem ser mais bem ilustradas pela figura 3. Elas aparecem porque a arquitetura de *cache* do processador força que transferências de dados só possam ser feitas a partir de uma das metades de uma linha de *cache*.

Figura 3: Restrições de alinhamento em uma linha de *cache* para o PowerPC 440 FP2. (a) mostra acessos de 64 *bits* (1 palavra de 64 *bits* ou duas palavras de 32 *bits*) e (b) mostra acessos de 128 *bits* (2 palavras de 64 *bits*).

Se as restrições não forem seguidas, o tempo para que a operação termine aumenta muito (fica da ordem de milhares de ciclos, contra alguns ciclos se as restrições forem atendidas), já que é gerada uma interrupção de alinhamento e o *software* deve forçar o alinhamento dos dados de forma a atender às restrições.

O conjunto de *kernels* utilizados para a avaliação de desempenho da tríade arquitetura-compilador-algoritmo faz parte do BLAS (*Basic Linear Algebra Subprograms*) [4] que, como o próprio nome diz, é um conjunto de rotinas básicas de álgebra linear. Os *kernels* utilizados foram o daxpy ( $y[n] = a * x[n] + y[n]$ , onde  $x$  e  $y$  são vetores), dgemv ( $y[m] = y[m] + A[m][n] * x[n]$ , onde  $x$  e  $y$  são vetores e  $A$  é uma matriz) e dgemm ( $C[m][n] = C[m][n] + A[m][k] * B[k][n]$ , onde  $A$ ,  $B$  e  $C$  são matrizes). Esses *kernels* foram executados sobre um simulador baseado em descrição de *hardware* e o modelo simulado inclui processador e unidade de ponto flutuante.

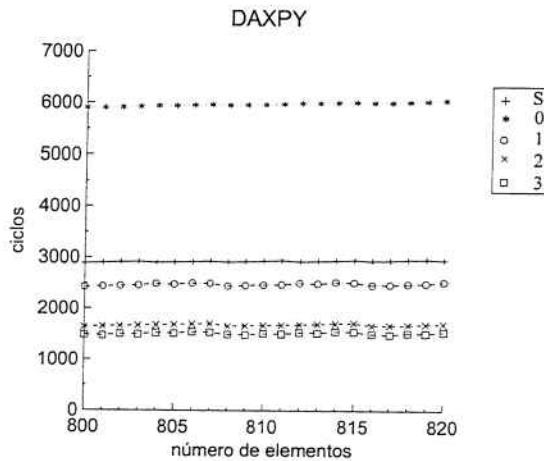

Um dos resultados obtidos pode ser observado na figura 4.

A versão s e a versão 0 são o código do daxpy sem nenhuma otimização. A única diferença entre elas é o compilador com que cada uma é compilada. A versão s é gerada com o compilador normalmente utilizado para gerar código para uma unidade PowerPC 440 FPU padrão. A versão 0 é gerada com o compilador otimizado para a unidade PowerPC 440 FP2. Esse versão tem uma performance inferior porque o compilador não tem informações de alinhamento sobre os vetores do *kernel*. Como se pode observar, o desempenho melhora na versão 1, em que são dadas ao compilador informações

Figura 4: Resultados para o *kernel daxpy* para uma faixa contígua de tamanhos de problema (800-820)

sobre alinhamento e sobreposição de vetores. No caso da versão 2, além dessas informações, o *unrolling* e o *scheduling* são feitos manualmente em linguagem C e o desempenho apresentado melhora um pouco mais. Na versão 3, os comandos em linguagem C são substituídos por comandos que controlam as instruções *assembly* geradas. O desempenho, porém, não é significativamente melhor do que na versão 2, o que mostra que o compilador fez um bom trabalho em escolher as instruções *assembly* a serem utilizadas na versão 2.

Os experimentos mostraram que a unidade pode atingir ganhos significativos em desempenho se devidamente programada.

Os resultados indicam que o compilador é capaz de aproveitar os novos recursos da unidade de ponto flutuante quando alimentado com dados sobre alinhamento e sobreposição de vetores e matrizes, principalmente para *kernels* mais simples, com poucos aninhamentos.

O compilador ainda encontra dificuldades em otimizar códigos mais complicados, com vários níveis de aninhamento. É possível, porém, gerar código otimizado para a unidade com o auxílio do recurso de *intrinsics* do compilador, onde o programador tem um maior controle sobre o código de baixo nível gerado, podendo escolher diretamente a seqüência de instruções *assembly* a serem utilizadas em determinados trechos do programa.

## 4 Rede de Interconexão Toroidal

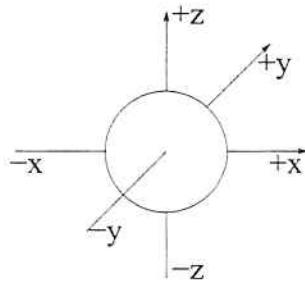

Numa das máquinas Blue Gene, a rede de interconexão normalmente utilizada para troca de dados de aplicações é a rede toroidal. Assim, cada uma das células é ligada a suas vizinhas através de seis *links*, como mostrado na figura 5. Todas as células responsáveis pela computação de aplicações serão interligadas em uma topologia toroidal de três dimensões.

Os pacotes têm formato proprietário e seu roteamento é feito por *hardware*. Cada pacote tem tamanho fixo de 256 *bytes* e cabeçalho de *hardware* de 8 *bytes*, incluído no pacote. O dispositivo de comunicação da rede toroidal é mapeado em memória.

Todas as transmissões e recepções entre processador e dispositivo de comunicação devem ser feitos em operações de 128 *bits*, ou 16 *bytes*. Assim, toda a interface entre processador e dispositivo é feita através da unidade de ponto flutuante dupla, a única unidade capaz de fazer transferências de dados tão largas.

Como as transmissões são feitas em blocos de 16 *bytes* e o cabeçalho de *hardware* só ocupa 8 *bytes*,

Figura 5: *Links* (com direção e sentido) de uma célula

decidiu-se utilizar os 8 *bytes* seguintes, já na área de dados, como cabeçalho de *software*. Assim, a primeira parte transmitida de um pacote inclui apenas cabeçalhos e através do cabeçalho de *software* pode-se passar informações a respeito dos dados sendo transmitidos.

O roteamento pode ser feito em modo determinístico, ou seja, é possível determinar qual o caminho seguido pelo pacote da origem para o destino. Outro modo de roteamento é o dinâmico e, nesse caso, não se pode determinar qual o caminho seguido por um pacote: ele depende do tráfego nos *links* de cada uma das células por onde o pacote passa. O modo de roteamento é determinado através de configurações feitas via *software* no cabeçalho do pacote.

Podem-se configurar outras características de roteamento através do cabeçalho do pacote como, por exemplo, os chamados *hint bits*. Os *hint bits* são destinados a instruir o *hardware* a enviar o pacote em um determinado sentido preferencial.

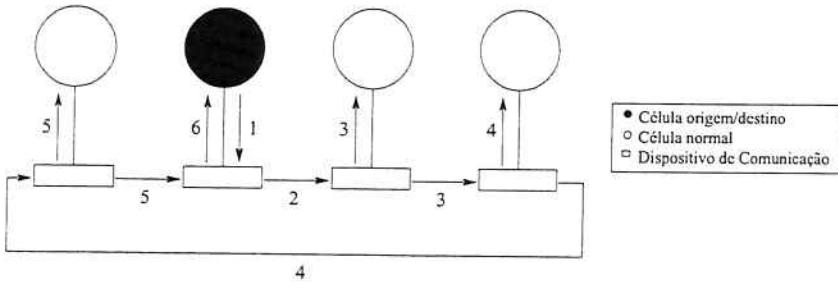

Outra característica interessante disponível através dessa rede de interconexão é o *multicast* em linha. De acordo com um *bit* configurável do cabeçalho, o chamado *deposit bit*, pode-se instruir o *hardware* a depositar o pacote em cada uma das células por onde o pacote passa até alcançar seu destino.

Esse tipo de operação, porém, só pode ser feita se o caminho que o pacote segue é uma linha, sem mudança de direção. Assim, só se pode enviar pacotes *multicast* se a origem e o destino estiverem em uma mesma linha do toróide.

Como para cada par origem-destino em uma direção do toróide há duas formas de atingir o destino saindo da origem (sentido positivo ou negativo), usa-se os *hint bits* para especificar qual dos caminhos devem ser seguidos.

Como cada direção do toróide está fechada em anel, pode-se, também, enviar pacotes para todas as células em uma linha. Basta que uma célula envie um pacote para si mesma. O *hardware* envia o pacote à célula vizinha, que copia o pacote para si e também o envia à próxima célula. Quando o pacote chega a um extremo, ele é enviado ao outro extremo, dando a volta no anel. O processo se repete até que o pacote atinja a célula originadora (que é o próprio destino). Assim, pode-se fazer um *multicast* total na linha, como mostra a figura 6.

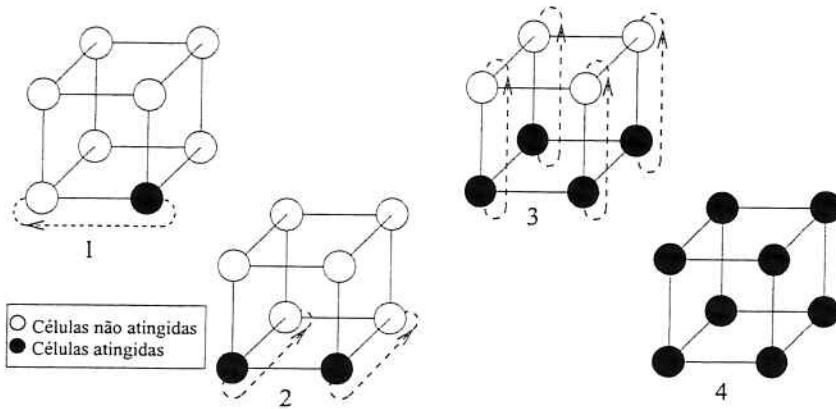

Apesar da limitação de manter o pacote em uma linha quando se usa os *deposit bits*, ainda é possível fazer *broadcasts* que atinjam todas as células, com algum suporte de *software*. Basta para isso que se marque o pacote como *broadcast* em algum campo da área de dados e se envie esse pacote com um *multicast* em linha em uma direção (suponhamos a direção x). Assim, todas as células daquela linha recebem esse pacote. Em seguida, o *software* verifica que aquele é um pacote de *broadcast* e o envia como *multicast* em linha em uma outra direção (digamos que seja a direção y). Assim, todos os pacotes ao longo de todos os anéis da direção inicial (x) recebem uma cópia do pacote. O *software* deve entrar novamente em ação e enviar agora um pacote de *multicast* em linha na direção restante (z, nesse caso). Dessa forma, cada uma das células do sistema recebe uma cópia do pacote inicial. O processo de *broadcast* descrito acima está ilustrado na figura 7.

Figura 6: *Multicast* completo em linha: os números mostram o caminho do pacote, partindo da célula origem, sendo depositada e reenviada em cada uma das outras células e voltando para a célula inicial, que também é o destino.

Figura 7: *Broadcast* com o auxílio de *software*: quatro etapas. (1) dados saem da origem, (2) dados terminam de percorrer eixo x, (3) dados terminam de percorrer eixo y e (4) dados terminam de percorrer eixo z.

O desempenho dessa rede de interconexão foi avaliado utilizando-se um simulador de sistema completo especialmente desenvolvido para a máquina. Ele modela várias células e a interconexão que as liga e é capaz de efetivamente simular a troca de dados entre elas pela rede. Assim, é possível executar aplicações paralelas que se utilizem da rede de interconexão para troca de dados e colher informações sobre elas com o simulador.

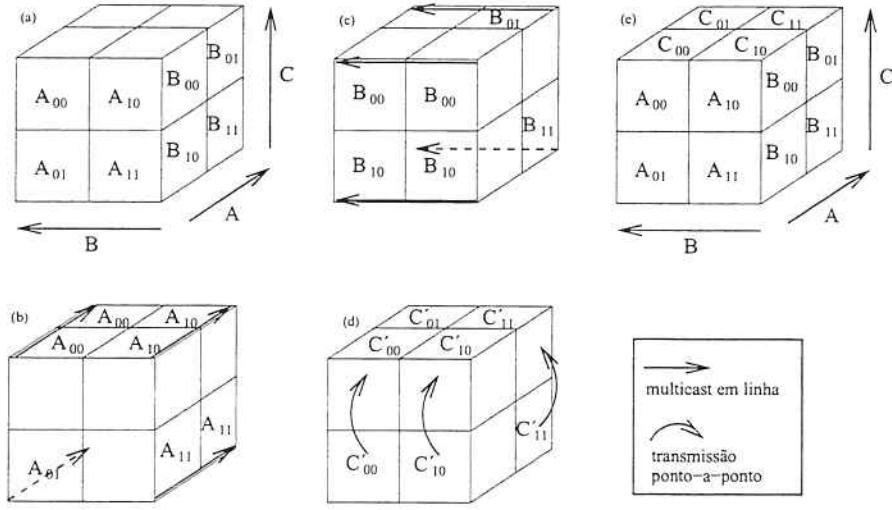

A aplicação selecionada para a avaliação foi a multiplicação tridimensional de matrizes, adaptada de [1]. Essa aplicação tira proveito do recurso de *multicast* em linha ao distribuir as matrizes no início da computação. A figura 8 mostra como o algoritmo funciona.

A operação a ser feita é  $C = C + A * B$ , onde  $A$  é uma matriz de dimensões  $M \times K$ ,  $B$  é uma matriz de dimensões  $K \times N$  e  $C$  é uma matriz de dimensões  $M \times N$ .  $A$  é dividida em submatrizes  $A_{00}$ ,  $A_{01}$ ,  $A_{10}$  e  $A_{11}$ , cada uma delas de dimensões  $\frac{M}{p} \times \frac{K}{p}$ , onde  $p$  é o número de células presentes em uma das arestas do cubo, ou  $m \times k$ . Em seguida, essas submatrizes são distribuídas entre as quatro células de uma das faces do cubo.  $B$  é dividida da mesma forma e distribuída em uma face ortogonal à face de  $A$ . A matriz  $A$  deve ser colocada de forma transposta em sua face, para que suas linhas ocupem colunas ao longo da face e as multiplicações entre partes de  $A$  e  $B$  possam ser feitas de forma mais simples, elemento a elemento em colunas. Essa distribuição pode ser observada na figura 8(a). A matriz  $C$  inicial também é dividida e colocada na base do cubo, na direção ortogonal

Figura 8: Algoritmo de multiplicação de matrizes tridimensional

às duas primeiras. Passa-se, então, à fase de distribuição dos elementos. As células pertencentes às faces de  $A$  fazem um *multicast* em linha com a sua submatriz, na reta perpendicular à face em que estão situadas, conforme é mostrado na figura 8(b). Simultaneamente, o mesmo acontece com as submatrizes contidas células da matriz  $B$ , como mostrado na figura 8(c). Em seguida, as células da base, que contêm elementos de  $A$ ,  $B$  e  $C$  (inicial) iniciam a computação. Quando a computação termina, essas células enviam o resultado  $C'$  apenas para as células diretamente acima delas, como mostrado na figura 8(d). Essas células, por sua vez, dão início à sua parte da computação. Quando a computação termina nas células do topo, o resultado está distribuído entre as células pertencentes à face do topo do cubo, como mostrado na figura 8 (e).

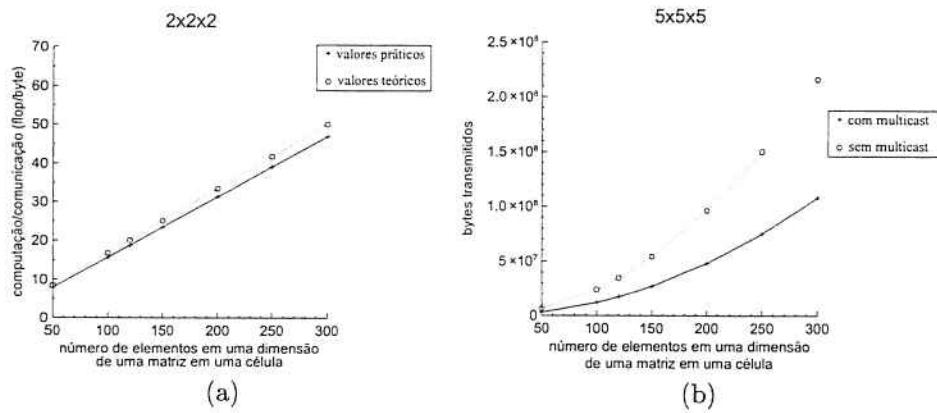

A figura 9 mostra alguns dos resultados obtidos.

Figura 9: (a)Resultados para o **dgemm** tridimensional com número de células fixo e variação do tamanho do problema (b)Comparação entre desempenho de sistemas que não dispõem do *multicast* em linha e de sistemas que dispõem do recurso

Foi possível observar pelos experimentos (fig. 9-a) que o *overhead* causado pelo cabeçalho do

pacote de dados é relativamente baixo, não tendo um impacto significativo no desempenho do sistema.

Outro resultado importante é que o *multicast* em linha é uma grande ferramenta para algoritmos tridimensionais onde uma informação precisa ser replicada em um subconjunto de células, pois evita que seja necessário transmitir essa informação várias vezes (fig. 9-b). Vale ressaltar que o *multicast* em linha diminui a quantidade de comunicação necessária para a resolução do problema. Diminuindo a quantidade de informações enviadas, ganha-se tempo de processamento para a computação propriamente dita, tempo esse que estaria sendo utilizado para o envio das informações. É importante perceber que não necessariamente se diminui a ocupação nos *links* de comunicação, já que a informação transmitida por *multicast* trafega da mesma forma pelos *links*, ao longo de todas as células envolvidas.

## 5 Conclusões e Trabalhos Futuros

Os simuladores mostraram-se ferramentas muito valiosas para estudos de avaliação de desempenho.

Para este estudo foram utilizados diferentes simuladores para diferentes propósitos. Cada simulador tem seus pontos fortes e fracos, sendo úteis para obter resultados específicos diferentes.

Foi possível verificar que o Cyclops é capaz, na prática, de atingir os níveis teóricos de banda sustentável de memória, podendo ser comparado a máquinas comerciais topo-de-linha. O único fator limitante para o uso do *chip* individualmente é a quantidade de memória disponível. Assim, o uso do *chip* para aplicações paralelas que utilizam poucos dados em cada célula parece ser indicado.

A unidade de ponto flutuante dupla estudada pode ser bastante utilizada para aplicações científicas. Ela provê uma maneira eficiente de aumentar o desempenho desse tipo de aplicação, sem aumentar muito a complexidade do *hardware*.

Porém, é muito importante que haja suporte de ferramentas para a geração de código para essa unidade. O compilador estudado é bastante eficiente para *kernels* simples. Conforme a complexidade dos *kernels* aumenta, o compilador apresenta mais dificuldades para gerar código eficiente.

Cabe, então, ao programador otimizar o código manualmente para a unidade, tarefa suportada pelo compilador através do recurso chamado de *intrinsics*.

A topologia toroidal mostrou-se adequada para a computação tridimensional de multiplicação de matrizes. Outras aplicações adequadas ao conceito de computação celular também parecem se adequar à topologia. O *overhead* observado não causa impacto significativo no desempenho como um todo.

O recurso de *multicast* em linha mostrou-se bastante eficiente e útil para aplicações onde é necessário transmitir a mesma informação para diversas células.

No caso do Cyclops, ainda é necessário estudar outros aspectos que não apenas a banda de memória atingida pelo sistema.

Outros benchmarks relacionados a aplicações científicas podem ser utilizados, como o BLAS, para a avaliação do compartilhamento das unidades de ponto flutuante entre as *threads*.

Além disso, o recurso de barreiras rápidas implementadas em *hardware* pode ser mais explorado utilizando aplicações altamente paralelizáveis que necessitem de sincronização.

No caso da unidade de ponto flutuante dupla, pode-se continuar o estudo com *kernels* que utilizem operações complexas, como por exemplo o zdgemm.

*Kernels* de álgebra linear esparsa, ou mesmo outros *kernels* bastante utilizados em aplicações científicas, como por exemplo o FFT (*Fast Fourier Transforms*), podem também ser utilizados para aprofundar o estudo.

O estudo da rede de topologia toroidal, pode ser aprofundado utilizando outros *kernels* científicos paralelizáveis.

Se uma biblioteca MPI for desenvolvida para uso sobre essa rede (como planejado), um estudo interessante é a implementação do dgemm tridimensional sobre essa nova biblioteca, para avaliar o *overhead* introduzido por ela. Ainda se pode utilizar o *benchmark* NAS [9], criado pela NASA, para

avaliar os ganhos com a biblioteca MPI sobre a rede de topologia toroidal em relação a uma rede Ethernet.

Para avaliar o desempenho do conjunto unidade de ponto flutuante e rede de topologia toroidal, ainda se pode utilizar aplicações de processamento sísmico, química computacional e modelamento de clima do SPEChpg96 [11] (*Standard Performance Evaluation Corporation: High Performance Group*), kernels adaptados como a FFT complexa unidimensional e a decomposição LU blocada do SPLASH [12] (*Stanford Parallel Applications for Shared Memory*) e aplicações adaptadas também do SPLASH como simulação de oceanos e simulação de água com ou sem estruturas de dados especiais.

## Referências

- [1] AGARWAL, R. C., BALLE, S. M., GUSTAVSON, F. G., JOSHI, M., AND PALKAR, P. A three-dimensional approach to parallel matrix multiplication. *IBM Journal of Research and Development* 39, 5 (1995).

- [2] ALLEN, F., ET AL. Blue Gene: A vision for protein science using a petaflop supercomputer. *IBM Systems Journal* 40, 2 (2001), 310–328.

- [3] ALMASI, G., ET AL. Cellular supercomputing with system-on-a-chip. In *ISSCC 2002 Proceedings* (San Francisco, California, USA, 2002), IBM T.J.Watson Research and IBM Enterprise Server Group.

- [4] DONGARRA, J. J., DUFF, I. S., SORENSEN, D. C., AND VAN DER VORST, H. A. *Solving Linear Systems on Vector and Shared Memory Computers*. Society for Industrial and Applied Mathematics, 1991.

- [5] HERROD, S. A. *Using Complete Machine Simulation to Understand Computer System Behavior*. PhD thesis, Stanford University, 1998.

- [6] J.LERNER, E. Cellular architecture builds next generation supercomputers. *Think Research 1* (June 2002).

- [7] MCCALPIN, J. D. Sustainable memory bandwidth in current high performance computers, 1995. <http://home.austin.rr.com/mccalpin/papers/bandwidth/>.

- [8] MUKHERJEE, S. S., ADVE, S. V., AUSTIN, T., EMER, J., AND MAGNUSSON, P. S. Performance simulation tools. *Computer Magazine* 1 (Feb. 2002).

- [9] NAS parallel benchmarks. <http://www.nas.nasa.gov/Software/NPB>.

- [10] SIPPER, M. The emergence of cellular computing. *Computer Magazine* 1 (July 1999).

- [11] Spec benchmarks. <http://www.specbench.org>.

- [12] Splash-2: Stanford parallel applications for shared memory. <http://www-flash.stanford.edu/apps/SPLASH/>.

- [13] Memory bandwidth: STREAM benchmark performance results. <http://www.cs.virginia.edu/stream/ref.html>.

## BOLETINS TÉCNICOS - TEXTOS PUBLICADOS

- BT/PCS/9301 - Interligação de Processadores através de Chaves Ómicron - GERALDO LINO DE CAMPOS, DEMI GETSCHKO

- BT/PCS/9302 - Implementação de Transparência em Sistema Distribuído - LUÍSA YUMIKO AKAO, JOÃO JOSÉ NETO

- BT/PCS/9303 - Desenvolvimento de Sistemas Especificados em SDL - SIDNEI H. TANO, SELMA S. S. MELNIKOFF

- BT/PCS/9304 - Um Modelo Formal para Sistemas Digitais à Nível de Transferência de Registradores - JOSÉ EDUARDO MOREIRA, WILSON VICENTE RUGGIERO

- BT/PCS/9305 - Uma Ferramenta para o Desenvolvimento de Protótipos de Programas Concorrentes - JORGE KINOSHITA, JOÃO JOSÉ NETO

- BT/PCS/9306 - Uma Ferramenta de Monitoração para um Núcleo de Resolução Distribuída de Problemas Orientado a Objetos - JAIME SIMÃO SICHMAN, ELERI CARDOSO

- BT/PCS/9307 - Uma Análise das Técnicas Reversíveis de Compressão de Dados - MÁRIO CESAR GOMES SEGURA, EDIT GRASSIANI LINO DE CAMPOS

- BT/PCS/9308 - Proposta de Rede Digital de Sistemas Integrados para Navio - CESAR DE ALVARENGA JACOBY, MOACYR MARTUCCI JR.

- BT/PCS/9309 - Sistemas UNIX para Tempo Real - PAULO CESAR CORIGLIANO, JOÃO JOSÉ NETO

- BT/PCS/9310 - Projeto de uma Unidade de Matching Store baseada em Memória Paginada para uma Máquina Fluxo de Dados Distribuído - EDUARDO MARQUES, CLAUDIO KIRNER

- BT/PCS/9401 - Implementação de Arquiteturas Abertas: Uma Aplicação na Automação da Manufatura - JORGE LUIS RISCO BECERRA, MOACYR MARTUCCI JR.

- BT/PCS/9402 - Modelamento Geométrico usando do Operadores Topológicos de Euler - GERALDO MACIEL DA FONSECA, MARIA ALICE GRIGAS VARELLA FERREIRA

- BT/PCS/9403 - Segmentação de Imagens aplicada a Reconhecimento Automático de Alvos - LEONCIO CLARO DE BARROS NETO, ANTONIO MARCOS DE AGUIRRA MASSOLA

- BT/PCS/9404 - Metodologia e Ambiente para Reutilização de Software Baseado em Composição - LEONARDO PUJATTI, MARIA ALICE GRIGAS VARELLA FERREIRA

- BT/PCS/9405 - Desenvolvimento de uma Solução para a Supervisão e Integração de Células de Manufatura Discreta - JOSÉ BENEDITO DE ALMEIDA, JOSÉ SIDNEI COLOMBO MARTINI

- BT/PCS/9406 - Método de Teste de Sincronização para Programas em ADA - EDUARDO T. MATSUDA, SELMA SHIN SHIMIZU MELNIKOFF

- BT/PCS/9407 - Um Compilador Paralelizante com Detecção de Paralelismo na Linguagem Intermediária - HSUEH TSUNG HSIANG, LÍRIA MATSUMOTO SAITO

- BT/PCS/9408 - Modelamento de Sistemas com Redes de Petri Interpretadas - CARLOS ALBERTO SANGIORGIO, WILSON V. RUGGIERO

- BT/PCS/9501 - Síntese de Voz com Qualidade - EVANDRO BACCI GOUVÉA, GERALDO LINO DE CAMPOS

- BT/PCS/9502 - Um Simulador de Arquiteturas de Computadores "A Computer Architecture Simulator" - CLAUDIO A. PRADO, WILSON V. RUGGIERO

- BT/PCS/9503 - Simulador para Avaliação da Confiabilidade de Sistemas Redundantes com Reparo - ANDRÉA LUCIA BRAGA, FRANCISCO JOSÉ DE OLIVEIRA DIAS

- BT/PCS/9504 - Projeto Conceitual e Projeto Básico do Nível de Coordenação de um Sistema Aberto de Automação, Utilizando Conceitos de Orientação a Objetos - NELSON TANOMARU, MOACYR MARTUCCI JUNIOR

- BT/PCS/9505 - Uma Experiência no Gerenciamento da Produção de Software - RICARDO LUIS DE AZEVEDO DA ROCHA, JOÃO JOSÉ NETO

- BT/PCS/9506 - MétodOO - Método de Desenvolvimento de Sistemas Orientado a Objetos: Uma Abordagem Integrada à Análise Estruturada e Redes de Petri - KECHI HIRAMA, SELMA SHIN SHIMIZU MELNIKOFF

- BT/PCS/9601 - MOOPP: Uma Metodologia Orientada a Objetos para Desenvolvimento de Software para Processamento Paralelo - ELISA HATSUE MORIYA HUZITA, LÍRIA MATSUMOTO SATO

- BT/PCS/9602 - Estudo do Espalhamento Brillouin Estimulado em Fibras Ópticas Monomodo - LUIS MEREGE SANCHES, CHARLES ARTUR SANTOS DE OLIVEIRA

- BT/PCS/9603 - Programação Paralela com Variáveis Compartilhadas para Sistemas Distribuídos - LUCIANA BEZERRA ARANTES, LÍRIA MATSUMOTO SATO

- BT/PCS/9604 - Uma Metodologia de Projeto de Redes Locais - TEREZA CRISTINA MELO DE BRITO CARVALHO, WILSON VICENTE RUGGIERO

- BT/PCS/9605 - Desenvolvimento de Sistema para Conversão de Textos em Fonemas no Idioma Português - DIMAS TREVIZAN CHBANE, GERALDO LINO DE CAMPOS

- BT/PCS/9606 - Sincronização de Fluxos Multimídia em um Sistema de Videoconferência - EDUARDO S. C. TAKAHASHI, STEFANIA STIUBIENER

- BT/PCS/9607 - A importância da Completeza na Especificação de Sistemas de Segurança - JOÃO BATISTA CAMARGO JÚNIOR, BENÍCIO JOSÉ DE SOUZA

- BT/PCS/9608 - Uma Abordagem Paraconsistente Baseada em Lógica Evidencial para Tratar Exceções em Sistemas de Frames com Múltipla Herança - BRÁULIO COELHO ÁVILA, MÁRCIO RILLO

- BT/PCS/9609 - Implementação de Engenharia Simultânea - MARCIO MOREIRA DA SILVA, MOACYR MARTUCCI JÚNIOR

- BT/PCS/9610 - Statecharts Adaptativos - Um Exemplo de Aplicação do STAD - JORGE RADY DE ALMEIDA JUNIOR, JOÃO JOSÉ NETO

- BT/PCS/9611 - Um Meta-Editor Dirigido por Sintaxe - MARGARETE KEIKO IWAI, JOÃO JOSÉ NETO

- BT/PCS/9612 - Reutilização em Software Orientado a Objetos: Um Estudo Empírico para Analisar a Dificuldade de Localização e Entendimento de Classes - SELMA SHIN SHIMIZU MELNIKOFF, PEDRO ALEXANDRE DE OLIVEIRA GIOVANI

- BT/PCS/9613 - Representação de Estruturas de Conhecimento em Sistemas de Banco de Dados - JUDITH PAVÓN MENDONZA, EDIT GRASSIANI LINO DE CAMPOS

- BT/PCS/9701 - Uma Experiência na Construção de um Tradutor Inglês - Português - JORGE KINOSHITA, JOÃO JOSÉ NETO

- BT/PCS/9702 - Combinando Análise de "Wavelet" e Análise Entrópica para Avaliar os Fenômenos de Difusão e Correlação - RUI CHUO HUEI CHIOU, MARIA ALICE G. V. FERREIRA

- BT/PCS/9703 - Um Método para Desenvolvimento de Sistemas de Computacionais de Apoio a Projetos de Engenharia - JOSÉ EDUARDO ZINDEL DEBONI, JOSE SIDNEI COLOMBO MARTINI

- BT/PCS/9704 - O Sistema de Posicionamento Global (GPS)-e suas Aplicações - SÉRGIO MIRANDA PAZ, CARLOS EDUARDO CUGNASCA

- BT/PCS/9705 - METAMBI-OO - Um Ambiente de Apoio ao Aprendizado da Técnica Orientada a Objetos - JOÃO UMBERTO FURQUIM DE SOUZA, SELMA S. S. MELNIKOFF

- BT/PCS/9706 - Um Ambiente Interativo para Visualização do Comportamento Dinâmico de Algoritmos - IZAURA CRISTINA ARAÚJO, JOÃO JOSÉ NETO

- BT/PCS/9707 - Metodologia Orientada a Objetos e sua Aplicação em Sistemas de CAD Baseado em "Features" - CARLOS CÉSAR TANAKA, MARIA ALICE GRIGAS VARELLA FERREIRA

- BT/PCS/9708 - Um Tutor Inteligente para Análise Orientada a Objetos - MARIA EMÍLIA GOMES SOBRAL, MARIA ALICE GRIGAS VARELLA FERREIRA

- BT/PCS/9709 - Metodologia para Seleção de Solução de Sistema de Aquisição de Dados para Aplicações de Pequeno Porte - MARCELO FINGUERMAN, JOSÉ SIDNEI COLOMBO MARTINI

- BT/PCS/9801 - Conexões Virtuais em Redes ATM e Escalabilidade de Sistemas de Transmissão de Dados sem Conexão - WAGNER LUIZ ZUCCHI, WILSON VICENTE RUGGIERO

- BT/PCS/9802 - Estudo Comparativo dos Sistemas da Qualidade - EDISON SPINA, MOACYR MARTUCCI JR.

- BT/PCS/9803 - The VIBRA Multi-Agent Architecture: Integrating Purposive Vision With Deliberative and Reactive Planning - REINALDO A. C. BIANCHI , ANNA H. REALI C. RILLO, LELIANE N. BARROS

- BT/PCS/9901 - Metodologia ODP para o Desenvolvimento de Sistemas Abertos de Automação – JORGE LUIS RISCO BECCERRA, MOACYR MARTUCCI JUNIOR

- BT/PCS/9902 – Especificação de Um Modelo de Dados Bitemporal Orientado a Objetos – SOLANGE NICE ALVES DE SOUZA, EDIT GRASSIANI LINO DE CAMPOS

- BT/PCS/9903 – Implementação Paralela Distribuída da Dissecção Cartesiana Aninhada – HILTON GARCIA FERNANDES, LIRIA MATSUMOTO SATO

- BT/PCS/9904 – Metodologia para Especificação e Implementação de Solução de Gerenciamento – SERGIO CLEMENTE, TEREZA CRISTINA MELO DE BRITO CARVALHO

- BT/PCS/9905 – Modelagem de Ferramenta Hipermídia Aberta para a Produção de Tutoriais Interativos – LEILA HYODO, ROMERO TORI

- BT/PCS/9906 – Métodos de Aplicações da Lógica Paraconsistente Anotada de Anotação com Dois Valores-LPA2v com Construção de Algoritmo e Implementação de Circuitos Eletrônicos – JOÃO I. DA SILVA FILHO, JAIR MINORO ABE

- BT/PCS/9907 – Modelo Nebuloso de Confiabilidade Baseado no Modelo de Markov – PAULO SÉRGIO CUGNASCA, MARCO TÚLIO CARVALHO DE ANDRADE

- BT/PCS/9908 – Uma Análise Comparativa do Fluxo de Mensagens entre os Modelos da Rede Contractual (RC) e Colisões Baseada em Dependências (CBD) – MÁRCIA ITO, JAIME SIMÃO SICHMAN

- BT/PCS/9909 – Otimização de Processo de Inserção Automática de Componentes Eletrônicos Empregando a Técnica de Times Assíncronos – CESAR SCARPINI RABAK, JAIME SIMÃO SICHMAN

- BT/PCS/9910 – MIISA – Uma Metodologia para Integração da Informação em Sistemas Abertos – HILDA CARVALHO DE OLIVEIRA, SELMA S. S. MELNIKOFF

- BT/PCS/9911 – Metodologia para Utilização de Componentes de Software: um estudo de Caso – KAZUTOSI TAKATA, SELMA S. S. MELNIKOFF

- BT/PCS/0001 – Método para Engenharia de Requisitos Norteados por Necessidades de Informação – ARISTIDES NOVELLI FILHO, MARIA ALICE GRIGAS VARELLA FERREIRA

- BT/PCS/0002 – Um Método de Escolha Automática de Soluções Usando Tecnologia Adaptativa – RICARDO LUIS DE AZEVEDO DA ROCHA, JOÃO JOSÉ NETO

- BT/PCS/0101 – Gerenciamento Hierárquico de Falhas – JAMIL KALIL NAUFAL JR., JOÃO BATISTA CAMARGO JR.

- BT/PCS/0102 – Um Método para a Construção de Analisadores Morfológicos, Aplicado à Língua Portuguesa, Baseado em Autômatos Adaptativos – CARLOS EDUARDO DANTAS DE MENEZES, JOÃO JOSÉ NETO

- BT/PCS/0103 – Educação pela Web: Metodologia e Ferramenta de Elaboração de Cursos com Navegação Dinâmica – LUISA ALEYDA GARCIA GONZÁLEZ, WILSON VICENTE RUGGIERO

- BT/PCS/0104 – O Desenvolvimento de Sistemas Baseados em Componentes a Partir da Visão de Objetos – RENATA EVANGELISTA ROMARIZ RECCO, JOÃO BATISTA CAMARGO JÚNIOR

- BT/PCS/0105 – Introdução às Gramáticas Adaptativas – MARGARETE KEIKO IWAI, JOÃO JOSÉ NETO

- BT/PCS/0106 – Automação dos Processos de Controle de Qualidade da Água e Esgoto em Laboratório de Controle Sanitário – JOSÉ BENEDITO DE ALMEIDA, JOSÉ SIDNEI COLOMBO MARTINI

- BT/PCS/0107 – Um Mecanismo para Distribuição Segura de Vídeo MPEG – CÍNTIA BORGES MARGI, GRAÇA BESSAN, WILSON VICENTE RUGGIERO

- BT/PCS/0108 – A Dependence-Based Model for Social Reasoning in Multi-Agent Systems – JAIME SIMÃO SICHMAN

- BT/PCS/0109 – Ambiente Multilinguagem de Programação – Aspectos do Projeto e Implementação – APARECIDO VALDEMIR DE FREITAS, JOÃO JOSÉ NETO

- BT/PCS/0110 – LETAC: Técnica para Análise de Tarefas e Especificação de Fluxo de Trabalho Cooperativo – MARCOS ROBERTO GREINER, LUCIA VILELA LEITE FILgueiras

- BT/PCS/0111 – Modelagem ODP para o Planejamento de Sistemas de Potência – ANIRIO SALLES FILHO, JOSÉ SIDNEI COLOMBO MARTINI

- BT/PCS/0112 – Técnica para Ajuste dos Coeficientes de Quantização do Padrão MPEG em Tempo Real – REGINA M. SILVEIRA, WILSON V. RUGGIERO

- BT/PCS/0113 – Segmentação de Imagens por Classificação de Cores: Uma Abordagem Neural – ALEXANDRE S. SIMÕES, ANNA REALI COSTA

- BT/PCS/0114 – Uma Avaliação do Sistema DSM Nautilus – MARIO DONATO MARINO, GERALDO LINO DE CAMPOS

- BT/PCS/0115 – Utilização de Redes Neurais Artificiais para Construção de Imagem em Câmara de Cintilação – LUIZ SÉRGIO DE SOUZA, EDITH RANZINI

- BT/PCS/0116 – Simulação de Redes ATM – HSU CHIH WANG CHANG, WILSON VICENTE RUGGIERO

- BT/PCS/0117 – Application of Monoprocessed Architecture for Safety Critical Control Systems – JOSÉ ANTONIO FONSECA, JORGE RADY DE ALMEIDA JR.

- BT/PCS/0118 – WebBee – Um Sistema de Informação via WEB para Pesquisa de Abelhas sem Ferrão – RENATO SOUSA DA CUNHA, ANTONIO MOURA SARAIVA

- BT/PCS/0119 – Parallel Processing Applied to Robot Manipulator Trajectory Planning – DENIS HAMILTON NOMIYAMA, LÍRIA MATSUMOTO SATO, ANDRÉ RIYUITI HIRAKAWA

- BT/PCS/0120 – Utilização de Padrão de Arquitetura de Software para a Fase de Projeto Orientado a Objetos – CRISITINA MARIA FERREIRA DA SILVA, SELMA SHIN SHIMIZU MELNIKOFF

- BT/PCS/0121 – Agilizando Aprendizagem por Reforço Através do uso de Conhecimento sobre o Domínio – RENÉ PEGORARO, ANNA H. REALI COSTA

- BT/PCS/0122 – Modelo de Segurança da Linguagem Java Problemas e Soluções – CLAUDIO MASSANORI MATAYOSHI, WILSON VICENTE RUGGIERO

- BT/PCS/0123 – Proposta de um Agente CNM para o Gerenciamento Web de um Backbone ATM – FERNANDO FROTA REDÍGOLO, TEREZA CRISTINA MELO DE BRITO CARVALHO

- BT/PCS/0124 – Um Método de Teste de software Baseado em Casos Teste – SÉRGIO RICARDO ROTTA, KECHI HIRAMA

- BT/PCS/0201 – A Teoria Nebulosa Aplicada a uma Bicicleta Ergométrica para Fisioterapia – MARCO ANTONIO GARMS, MARCO TÚLIO CARVALHO DE ANDRADE

- BT/PCS/0202 – Synchronization Constraints in a Concurrent Object Oriented Programming Model – LAÍS DO NASCIMENTO SALVADOR, LÍRIA MATSUMOTO SATO

- BT/PCS/0203 – Construção de um Ambiente de Dados sobre um Sistema de Arquivos Paralelos – JOSÉ CRAVEIRO DA COSTA NETO, LIRIA MATSUMOTO SATO

- BT/PCS/0204 – Maestro: Um Middleware para Suporte a Aplicações Distribuídas Baseadas em Componentes de Software – CLÁUDIO LUÍS PEREIRA FERREIRA, JORGE LUÍS RISCO BECERRA

- BT/PCS/0205 - Sistemas de Automação dos Transportes (ITS) Descritos Através das Técnicas de Modelagem RM-OPD (ITU-T) e UML (OMG) – CLÁUDIO LUIZ MARTE, JORGE LUÍS RISCO BECERRA, JOSÉ SIDNEI COLOMBO

- BT/PCS/0206 – Comparação de Perfis de Usuários Coletados Através do Agente de Interface PersonalSearcher – GUSTAVO A. GIMÉNEZ LUGO, ANALÍA AMANDI, JAIME SIMÃO SICHMAN

- BT/PCS/0207 – Arquitetura Reutilizáveis para a Criação de Sistemas de Tutorização Inteligentes – MARCO ANTONIO FURLAN DE SOUZA, MARIA ALICE GRIGAS VARELLA FERREIRA

- BT/PCS/0208 – Análise e Predição de Desempenho de Programas Paralelos em Redes de Estações de Trabalho – LIN KUAN CHING, LIRIA MATSUMOTO SATO

- BT/PCS/0209 – Previsões Financeiras Através de Sistemas Neuronebulosos – DANIEL DE SOUZA GOMES, MARCO TÚLIO CARVALHO DE ANDRADE

- BT/PCS/0210 – Proposta de Arquitetura Aberta de Central de Atendimento – ANA PAULA GONÇALVES SERRA, MOACYR MARTUCCI JÚNIOR

- BT/PCS/0211 – Alternativas de Implementação de Sistemas Nebulosos em Hardware – MARCOS ALVES PREDEBON, MARCO TÚLIO CA.RVALHO DE ANDRADE

- BT/PCS/0212 – Registro de Imagens de Documentos Antigos – VALGUIMA VICTORIA VIANA ODAKURA MARTINEZ, GERALDO LINO DE CAMPOS

- BT/PCS/0213 – Um Modelo de Dados Multidimensional – PEDRO WILLEMSSENS, JORGE RADY DE ALMEIDA JUNIOR

- BT/PCS/0214 – Autômatos Adaptativos no Tratamento Sintático de Linguagem Natural – CÉLIA YUMI OKANO TANIWAKI, JOÃO JOSÉ NETO

- BT/PCS/0215 – Fatores e Subfatores para Avaliação da Segurança em Software de Sistemas Críticos – JOÃO EDUARDO PROENÇA PÁSCOA, JOÃO BATISTA CAMARGO JÚNIOR

- BT/PCS/0216 – Derivando um Modelo de Projeto a Partir de um Modelo de Análise, com Base em Design Patterns J2EE – SERGIO MARTINS FERNANDES, SELMA SHIN SHIMIZU MELNIKOFF

- BT/PCS/0217 – Domínios Virtuais para Redes Móveis Ad Hoc: Um Mecanismo de Segurança – LEONARDO AUGUSTO MARTUCCI, TEREZA CRISTINA DE MELO BRITO CARVALHO

- BT/PCS/0218 – Uma Ferramenta para a Formulação de Consultas Baseadas em Entidades e Papéis – ANDRÉ ROBERTO DORETO SANTOS, EDIT GRASSIANI LINO CAMPOS