## Comparative study of the proton beam effects between the conventional and Circular-Gate MOSFETs

K. Cirne <sup>a,c,\*</sup>, M.A.G. Silveira <sup>a</sup>, R.B.B. Santos <sup>a</sup>, S.P. Gimenez <sup>a</sup>, M.D.L. Barbosa <sup>b</sup>, M.H. Tabacniks <sup>b</sup>, N. Added <sup>b</sup>, N.H. Medina <sup>b</sup>, W.R. De Melo <sup>c</sup>, L.E. Seixas Jr. <sup>c</sup>, J.A. De Lima <sup>c</sup>

<sup>a</sup> Centro Universitário da FEI, São Bernardo do Campo, SP, Brazil

<sup>b</sup> Instituto de Física da USP (IFUSP), Universidade de São Paulo, São Paulo, SP, Brazil

<sup>c</sup> Centro de Tecnologia da Informação Renato Archer (CTI), IC Design House, Campinas, SP, Brazil

### ARTICLE INFO

#### Article history:

Available online 27 July 2011

#### Keywords:

Total Ionizing Dose (TID)

External proton beam

Circular-Gate MOSFET

Rectangular-Gate MOSFET

Integrated circuits

Radiation effects

Radiation hardening

### ABSTRACT

The study of ionizing radiation effects on semiconductor devices is of great relevance for the global technological development and is a necessity in some strategic areas in Brazil. This work presents preliminary results of radiation effects in MOSFETs that were exposed to 3.2 Grad radiation dose produced by a 2.6-MeV proton beam. The focus of this work was to electrically characterize a Rectangular-Gate MOSFET (RGT) and a Circular-Gate MOSFET (CGT), manufactured with the On Semiconductor 0.5 μm standard CMOS fabrication process and to verify a suitable geometry for space applications. During the experiment,  $I_{DS} \times V_{GS}$  curves were measured. After irradiation, the RGT off-state current ( $I_{OFF}$ ) increased approximately two orders of magnitude reaching practically the same value of the  $I_{OFF}$  in the CGT, which only doubled its value.

© 2011 Elsevier B.V. All rights reserved.

## 1. Introduction

As new technologies are developed and integrated circuits (ICs) are miniaturized, the concern with ionizing radiation effects has increased in the prototyping of analog and digital circuits [1]. The increasing need for radiation tolerant circuits, made the aerospace agencies and governments to encourage the scientific community to develop new techniques, fabrication processes, materials and devices that can mitigate the degradation of ionizing radiation (protons, heavy ions and electromagnetic waves) in semiconductor device parameters and possibly electrical failures [2].

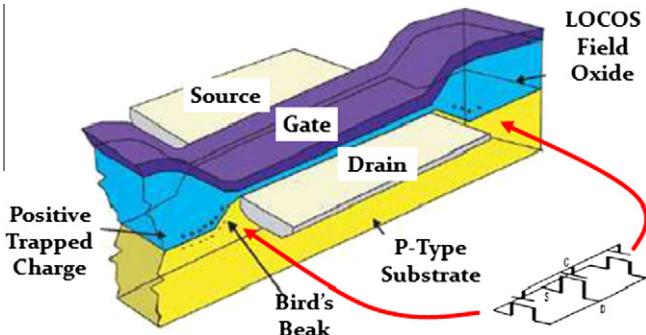

The total ionizing dose (TID), which is the accumulation of the ionizing dose over time, is one of the most common problems to which ICs are exposed in space environment and, possibly, also at ground level [3,4]. TID can cause the degradation of electrical parameters of the MOSFETs, depending on the region in which the positive charges are deposited in the device. If most of the positive charges are trapped in the gate oxide, there is a decrease in the threshold voltage ( $V_{TH}$ ) [3]. However, if most of the positive charges are trapped in the Silicon/Gate Oxide interface (Si/SiO<sub>2</sub>), there is an increase in the threshold voltage and in the subthreshold slope ( $S$ ) [3]. Additionally, most of the Rectangular-Gate transistors manufactured with the conventional CMOS process, suffer from the bird's

beak effect [3]. Fig. 1 presents a side cross section of a Rectangular-Gate transistor, indicating the bird's beak region. The bird's beak traps positive charges, thus inverting the p-type substrate, which leads to the creation of a parasitic channel between the drain and source contacts, even with no bias applied to the gate terminal, increasing the off-state current ( $I_{OFF}$ ) and the leakage current ( $I_{LEAK}$ ). In fact, the parasitic channel created by the bird's beak can be considered as a parasitic MOSFET in parallel to the prototyped MOSFET. Since we have two bird's beak per transistor, the RGT consists effectively of three MOSFETs in parallel.

Total dose effects can be mitigated through layout strategies, using Enclosed Layout Transistors (ELTs) [5], such as the Circular-Gate Transistor (CGT) [6]. In a CGT, the gate circumvents the internal region avoiding the appearance of a bird's beak structure.

This work presents an electrical characterization of a Rectangular-Gate transistor (RGT) and a Circular-Gate transistor (CGT), manufactured with the standard CMOS fabrication process AMI (On Semiconductor) of 0.5 μm, that were exposed to a 2.6-MeV external proton beam produced by the 1.7 MV Pelletron accelerator of the University of São Paulo. During the irradiation procedure, beam current was changed aiming different proton fluences and the samples were characterized electrically before, during and after the irradiation.

## 2. MOSFET prototyping

To attest the robustness of the Enclosed Layout Transistor (ELT) category, a Rectangular-Gate transistor (RGT) and a Circular-Gate

\* Corresponding author at: Centro de Tecnologia da Informação Renato Archer (CTI), IC Design House, Campinas, SP, Brazil.

E-mail address: [klauscirne@gmail.com](mailto:klauscirne@gmail.com) (K. Cirne).

Fig. 1. Side cutting of a conventional MOSFET, indicating the bird's beak region and its equivalent circuit [7].

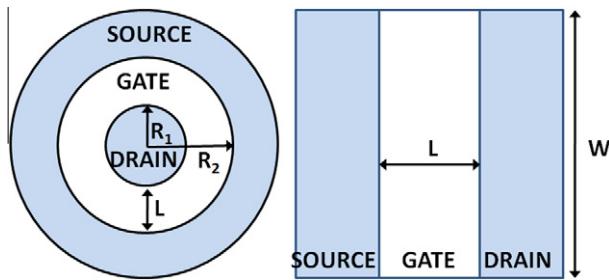

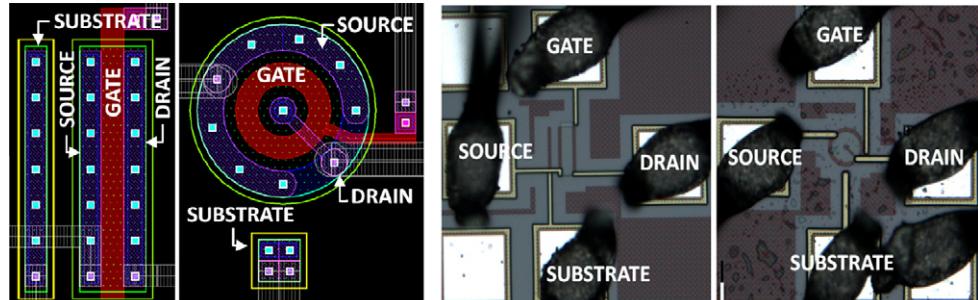

Fig. 2. Simplified layout of a CGT and of an RGT.

transistor (CGT) were prototyped for this experiment. Fig. 2 shows a simplified layout of a Circular-Gate transistor (Fig. 2a), and of a Rectangular-Gate transistor (Fig. 2b). In a CGT, channel length is

defined as  $L = R_2 - R_1$ , where  $R_1$  and  $R_2$  are the internal and the external radius of the CGT, respectively. Unlike the RGT, the CGT is an asymmetric transistor, since its internal and external regions present different areas and behave differently when biased in internal or external configurations [6]. However, the reduced CGT internal region, when configured as an internal drain is capable to reduce the stray capacitances. In order to compare the radiation effects between rectangular and circular shaped transistors, the effective CGT aspect ratio was used to prototype equivalent devices [8]:

$$\left(\frac{W}{L}\right)_{RGT} = \left[ \frac{2\pi}{\ln\left(\frac{R_2}{R_1}\right)} \right]_{CGT} \quad (1)$$

For the experiment, "N" type MOSFETs of a RGT and of a CGT geometries with channel length of 12  $\mu\text{m}$  were prototyped, using the design rules of the 0.5  $\mu\text{m}$  standard CMOS fabrication process of the AMI (On Semiconductor). Fig. 3 shows the RGT and the CGT layouts, as designed by IcStation software from Mentor Graphics (Fig. 3a) and their picture after manufacturing process (Fig. 3b).

### 3. Irradiation procedure

The transistors were directly exposed to 2.6-MeV proton beams with currents of 1 and 10 nA. During irradiation, several  $I_{DS} \times V_{GS}$  curves with  $V_{DS} = 100$  mV were measured, using an automatic measuring interface. Before and after irradiation procedure, the devices were electrically characterized using a semiconductor device analyzer. The CGT and the RGT were both exposed up to 3.2 Grad radiation dose, varying beam current and irradiation time.

Fig. 3. Layout of the RGT and the CGT implemented with the IcStation software and their correspondent device image after the manufacturing process.

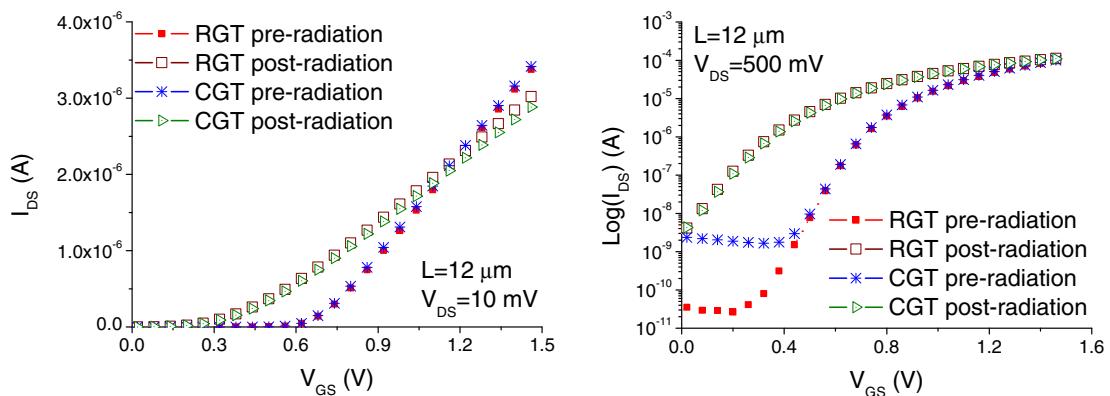

Fig. 4.  $I_{DS} \times V_{GS}$  curves for  $V_{DS} = 10$  mV of the RGT and the CGT and  $\log(I_{DS}) \times V_{GS}$  curves for  $V_{DS} = 500$  mV of the RGT and the CGT, respectively.

#### 4. Experimental results

In Fig. 4,  $I_{DS} \times V_{GS}$  curves with  $V_{DS} = 10$  mV (a) and the  $\log(I_{DS}) \times V_{GS}$  curves with  $V_{DS} = 500$  mV, measured before and after irradiation. The semiconductor parametric analyzer (Keithley 4200) is also shown. Although circular transistors tend to be more tolerant to ionizing irradiation, both the RGT and the CGT presented a variation of 350 mV of the threshold voltage, after being exposed to 3.2 Grad total dose. However, the off-state current and the leakage current of the CGT were practically not affected by the radiation, in contrast to the RGT, as shown in Fig. 4b. Since the Enclosed Layout Transistors (ELT) do not have the bird's beak region, they present a smaller degradation in the off-state current and in the subthreshold slope [3], compared to the conventional MOSFETs. It should be noticed that the RGT presented more than two orders of magnitude variation in the off-state current, reaching practically the same value than the CGT, which presented only a twofold increase in the off-state current after irradiation. This increment in the RGT's  $I_{OFF}$  is attributed to the accumulation of trapped positive charges in the bird's beak region, which leads to conduction of a leakage current between the drain and source contacts, even with no bias applied to the gate.

#### 5. Conclusions

A Rectangular-Gate transistor and a Circular-Gate transistor were prototyped, using 0.5  $\mu$ m standard CMOS fabrication process AMI (On Semiconductor) with a channel length of 12  $\mu$ m. These devices were exposed up to 3.2 Grad protons with 2.6 MV and electrically characterized before and after the irradiation exposure. The results show that the RGT and the CGT presented a variation of 350 mV in their threshold voltage. As expected, the RGT is strongly influenced by ionizing radiation due to the presence of the bird's

beak region, which leads to an increase of two orders of magnitude in the off-state current, reaching practically the same value of CGT  $I_{OFF}$ , that only doubled its magnitude and therefore can be used as an alternative device for spacial integrated circuits. Based on the experimental results, we can conclude that the CGT is more tolerant to proton beam irradiation, if compared to the RGT counterpart, regarding the same bias and irradiation conditions.

#### Acknowledgements

The authors would like to thank CNPq, CI Brasil and NAMITEC for the financial support and the CTI for packaging and testing the IC.

#### References

- [1] S. Duzellier, Radiation effects on electronic devices in space, *Aerosp. Sci. Technol.* 9 (2005) 93–99.

- [2] D.G. Mavis, D.R. Alexander, Employing radiation hardness by design techniques with commercial integrated circuit processes, in: 16th Digital Avionics Systems Conference, 1997, AIAA/IEEE.

- [3] H.J. Barnaby, Total-ionizing-dose effects in modern CMOS technologies, *IEEE Trans. Nucl. Sci.* 53 (6) (2006) 3103–3121.

- [4] H.J. Barnaby, R.D. Schrimpf, A.L. Sternberg, V. Berthe, C.R. Cirba, R.L. Pease, Proton radiation response mechanisms in bipolar analog circuits, *IEEE Trans. Nucl. Sci.* 48 (6) (2001) 2074–2080.

- [5] E. Simoen, J.M. Rafi, A. Mercha, C. Clayes, Total ionization dose damage in deep submicron partially depleted SOI MOSFETs induced by proton irradiation, *Solid-State Electron.* 48 (2004) 1045–1054.

- [6] S.P. Gimenez, R.M.G. Ferreira, J.A. Martino, Early voltage behavior in circular gate SOI nMOSFET using 0.13  $\mu$ m partially-depleted SOI CMOS Technology, in: Microelectronics Technology and Devices, ECS Transactions, 2006, Ouro Preto – MG, SBMICRO 2006, ECS Transactions, Washington, ECS 4 (2006) 309–318.

- [7] T.R. Balen, Efeitos da Radiação em Dispositivos Analógicos Programáveis (FPAAs) e Técnicas de Proteção, Doctor Degree Thesis, UFRGS, 2010.

- [8] J.P. Colinge, Silicon-On-Insulator Technology: Materials to VLSI, third ed., Kluwer Academic Publishers, 2004.