01/

05

---

---

## **DESENVOLVIMENTO DE UM AMBIENTE DE PROGRAMAÇÃO E SIMULAÇÃO DE ROBÔS MÓVEIS BASEADOS EM HARDWARE RECONFIGURÁVEL.**

**Jean Miler Scatena \***

e-mail: jscatena@icmc.usp.br

**Maria Stela Veludo de Paiva\*\***

e-mail: mstela@sel.eesc.usp.br

**Leandro Carlos Fernandes \***

**Eduardo Marques**

e-mail: (emarques, lnd@icm.usp.br)

\* Universidade de São Paulo / Instituto de Ciências Matemáticas e Computacionais,

São Carlos, Brasil

\*\* Universidade de São Paulo / Departamento de Engenharia Elétrica, São Carlos,

Brasil

---

**Abstract:** The objectif of this work is to present a tool for the development and validation of a self-configurable robot. This tool uses the FPGAs architecture, GNU GCC programming language and a Player/Stage simulator to create tasks or applications to these robots.

**Palavras Chaves:** Robôs Móveis, Hardware Reconfigurável, Sistemas Robóticos, Ambiente de Programação de Robôs Móveis, Robôs Móveis Autônomos.

### **Introdução**

As pesquisas desenvolvidas na área de robótica vêm sofrendo uma evolução propiciada pelo grande desenvolvimento da área de inteligência artificial, pois sem essa área os robôs serviriam apenas como robôs de chão de fábrica, os quais realizariam apenas uma única tarefa.

Seguindo essa evolução já se pode ver hoje os primeiros humanóides (robôs com aparência humana) desenvolvidos por empresas japonesas como a Sony e a Honda. Outro exemplo é o dos robôs que imitam animais como o cão Aibo da Sony [6], que é totalmente ajustável ao seu dono, podendo ser reprogramado pelo próprio usuário, possuindo também a capacidade de aprender na interação com o seu dono.

Cadastrado pelo

ICMC

11 p.

Recentemente uma nova área de pesquisa para os sistemas robóticos autônomos está se despondo, a área de sistemas robóticos auto-reconfiguráveis. O objetivo desta nova área é a de construir robôs autônomos e auto-suficientes, isto é, que tenham a capacidade de reconfigurar suas tarefas sem a intervenção humana. Para isso esses robôs deverão incluir um conjunto de módulos com tarefas previamente armazenadas, que permitirão a seleção automática de uma nova tarefa, a cada mudança de ação, sem a necessidade de intervenção humana e sem ter que serem desligados.

O presente trabalho enquadra-se nesta nova área e propõe um novo conceito de “criação” de sistemas robóticos, onde a estruturação de um robô é feita a partir de um sistema que engloba hardware reconfigurável, um ambiente de desenvolvimento de aplicações robóticas e um simulador do hardware, deixando de lado os sistemas comerciais prontos.

## Robôs

Ao se analisar a evolução dos chamados Robôs, é possível distinguir as diferentes aplicações desta palavra em suas mais diversas situações. A palavra Robô pode tanto ser aplicada *para máquinas independentes, como os braços mecânicos de uma fábrica* [1], quanto a um humanóide desenvolvido pela empresa Honda.

Em todas as aplicações empregadas à palavra Robô, merece uma maior atenção a área de robôs móveis, pois nessa área existe uma concentração de esforços para a introdução da capacidade de autonomia e mobilidade dos robôs, de maneira tal a reagirem adequadamente em um ambiente[1].

A adequação dos robôs móveis à vida cotidiana depende das tarefas que são realizadas de forma repetitiva e que não necessitam de grandes esforços intelectuais. Como exemplos práticos e cotidianos de tarefas que se adequariam às funcionalidades de um robô móvel pode-se citar: o transporte de materiais, combate a incêndios, desativação de explosivos, vigilância de armazéns, viagens submarinas, aeroespaciais e prestação de serviços, onde haja interação com pessoas para o auxílio de tarefas rotineiras [1].

Para a realização de tais tarefas o robô móvel deve ser capaz de perceber as circunstâncias ao seu redor, e a partir disto gerar ações que serão apropriadas para o ambiente e para os objetivos de seu sistema. As ações utilizadas neste(s) ambiente(s) são técnicas que usam vários recursos da computação, como por exemplo, a inteligência artificial, a qual fornece detalhes precisos do ambiente (mundo) em que o sistema está interagindo.

Os robôs móveis realizam somente tarefas específicas previamente programadas, enquanto que os robôs móveis reconfiguráveis possibilitam a reconfiguração de seus módulos de tarefas através de intervenções em seu sistema principal. Já os robôs auto-reconfiguráveis, que são a evolução dos robôs móveis reconfiguráveis, possuem a capacidade de alterar a sua programação de forma a atender uma nova tarefa sem a interferência humana. Dessa forma, a inclusão de auto-reconfiguração nos robôs móveis resulta num sistema robótico completo, capaz de realizar as mais diversas tarefas, sem que na mudança de uma tarefa para outra haja qualquer tipo de intervenção humana.

## **Hardware Reconfigurável**

Tendo em vista a utilização de sistemas baseados em hardware reconfigurável será apresentado a seguir este conceito.

O conceito de hardware reconfigurável surgiu após a evolução dos componentes eletrônicos e dos métodos de desenvolvimento de circuitos, sendo esses fatores uma influência direta na criação de novas soluções para as mais diversas áreas existentes [9, 10].

No conceito de componentes digitais, a evolução se deu dos transistores individuais para os circuitos integrados, inicialmente com os circuitos SSI (*Small Scale Integration*), e com o avanço tecnológico possibilitando uma maior integração num único *chip* vieram os circuitos MSI (*Medium Scale Integration*) seguidos pelos VLSI (*Very Large Scale Integration*). Acompanhando esta evolução iniciou-se a utilização de ferramentas EDA (Eletronic Design Automation), para simplificar e acelerar todo o ciclo do projeto, deixando com isso, de haver a necessidade de se desenhar portas lógicas individuais e planejar todas as suas interconexões [9, 10].

O projeto de desenvolvimento de ferramentas para auxiliar a elaboração de circuitos vem adquirindo importância cada vez maior, pois todas as mudanças na tecnologia de circuitos digitais tem exigido uma prototipação cada vez mais rápida, já que o ciclo de vida dos produtos modernos está se tornando cada vez mais curto em relação ao tempo necessário para o projeto e desenvolvimento dos mesmos [10].

É importante ressaltar que os Circuitos Integrados (CIs) digitais podem ser construídos utilizando-se várias tecnologias diferentes, sendo que a escolha da tecnologia adequada deve ser feita com base no tipo de projeto que se pretende executar.

A tecnologia que mais está se destacando no mercado mundial é a dos FPGAs (Field-Programmable Gate Arrays), pois a programação de um FPGA é realizada pelo próprio usuário final ou em um laboratório de desenvolvimento, sem que haja a necessidade da construção física do chip propriamente dito. Para isso, utiliza-se uma ferramenta EDA para criar a diagramação do circuito, juntamente com a simulação de sinais e tempos de acesso. Após a finalização dos testes e validação do esquemático do circuito, é realizada a programação lógica do FPGA.

Devido a esta nova tecnologia “nasceu” à computação reconfigurável, que permite ao usuário criar uma solução para suas necessidades e programar esta solução em um FPGA. Essa nova área, computação reconfigurável, apresenta-se como uma tecnologia inovadora, pois tem se destacado pelas suas características de desenvolvimento e construção, tanto no campo industrial, como no campo acadêmico, o que pode ser comprovado pelos diversos trabalhos realizados na construção de arquiteturas reconfiguráveis, destacando-se desde simples tocadores de MP3 e celulares, até complexos sistemas de robótica, Inteligência Artificial, sistemas de aeronaves e carros, entre vários outros.

Apesar de sua vasta gama de aplicações, a computação reconfigurável ainda é uma área em desenvolvimento, diferente de arquitetura de computadores, onde os conceitos e mecanismos tem sido longamente testados e comprovados. Portanto, definir e validar esses tópicos em computação reconfigurável torna-se atualmente um desafio para os pesquisadores. Contudo há um grande interesse em tornar esta

tecnologia um padrão mundial. Grandes empresas vêm utilizando essa tecnologia e aprovando-a em sua totalidade motivando assim a sua padronização [9].

### Field Programmable Gate Array (F.P.G.A)

A computação reconfigurável nasceu da estruturação de uma nova tecnologia denominada FPGA (Field Programmable Gate Array). Porém, o que vem a ser uma FPGA?

Para que se possa entender melhor o que vem a ser uma FPGA, é necessário retornar a alguns anos atrás, quando a maioria dos hardwares bem como suas funções lógicas eram fixas e não podiam ser modificadas, sendo que com essas características era impossível reaproveitar um hardware depois do *chip* ter sido confeccionado. Com as FPGAs isso tornou-se possível.

Uma F.P.G.A possui um sistema de funções lógicas e blocos lógicos alteráveis, que inclui também as conexões entre esses blocos. Com essa nova forma de organização estrutural, os blocos lógicos de um FPGA podem ser re-escritos e reprogramados repetidamente, muito depois do chip ter sido produzido em uma fábrica [12].

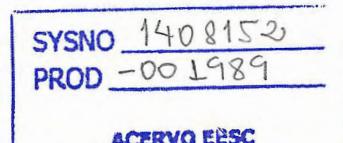

A arquitetura básica de um FPGA consiste de um arranjo 2-D de blocos lógicos, onde a comunicação entre os blocos é realizada através de recursos de interconexão, sendo a borda externa constituída por um arranjo de blocos especiais capazes de realizar operações de entrada e saída (I/O). Uma arquitetura típica de um FPGA pode ser visualizada na Figura 1.

Figura 1: Estrutura básica de um FPGA [11]

Os principais fabricantes de FPGAs são:

- *Altera* - os chips da Altera apresentam um altíssimo nível de integração, o que permite que sistemas complexos sejam implementados em um único dispositivo e possuem um acentuado desempenho, possibilitando assim, uma alta flexibilidade de projeto e eficiência para aplicações SOC (System on a Chip) de alto desempenho [7]. As mais modernas famílias de FPGAs desenvolvida pela Altera são as famílias STRATIX e CYCLONE.

- *Xilinx* - a tradicional fabricante de FPGAs Xilinx atualmente trabalha com as famílias Virtex IV e SPARTAN. Essas famílias são especialmente desenvolvidas para possibilitar um rápido desenvolvimento em duas das mais

desafiadoras áreas da tecnologia: a comunicação de dados e o processamento de sinais digitais [8];

- *Actel* - a mais moderna família de FPGAs desenvolvida pela Actel é a família PROASIC. Os chips PROASIC são baseados na tecnologia antifuse e, têm como características básicas o alto desempenho, o baixo custo e consumo de energia.

Com a implantação dessa nova tecnologia, surgem novos termos e conceitos, como por exemplo, o termo IP (Intellectual Property) que significa a venda de uma nova tecnologia ou ferramenta baseada em FPGA, a qual foi implementada por um desenvolvedor, que realizará o comércio da sua propriedade intelectual e não de um produto final. Podemos dizer que os IPs são bibliotecas de dispositivos que podem ser agregados a um produto final.

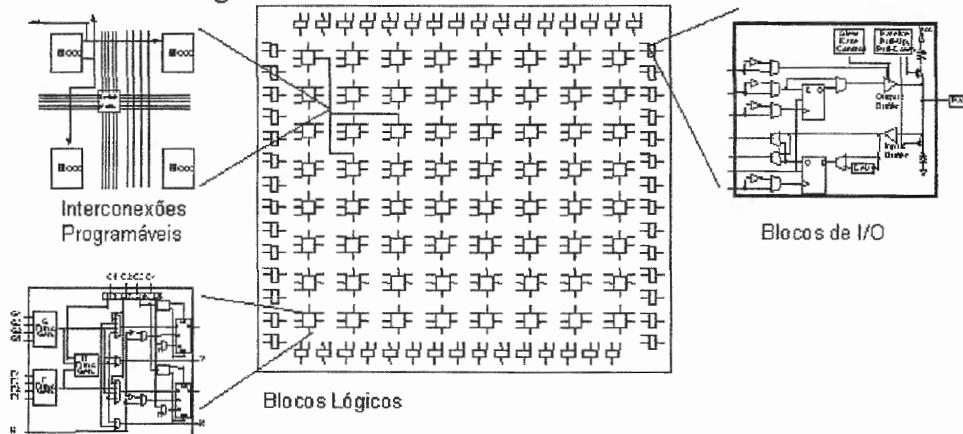

Outro termo também muito discutido em FPGAs é o termo reconfiguração dinâmica, ou também conhecida com auto-reconfiguração. Isto implica que o sistema desenvolvido possui a capacidade de alterar seu conteúdo programado totalmente ou parcialmente, sem afetar a funcionalidade do sistema, usando um mecanismo transparente, de forma que o sistema não precisa parar a sua execução enquanto o FPGA é reconfigurado [13].

Esse tipo de recurso pode ser classificado conforme ilustrado na Figura 2 [14].

Figura 2: Classificação de FPGAs de acordo com sua reconfigurabilidade

As FPGAs podem ser classificadas de acordo com sua reconfigurabilidade, da seguinte forma (figura 2):

- *Reconfiguração Parcial*: essa reconfiguração é caracterizada como parcial se um dispositivo aceita uma reconfiguração seletivamente, ou seja, uma parte do dispositivo é reconfigurado enquanto o resto permanece inativo, porém a parte que não será reconfigurada permanece intacta sem nenhuma modificação;

- *Reconfiguração Dinâmica*: os FPGAs são classificados como dinamicamente reconfiguráveis se seus circuitos internos de armazenamento podem ser atualizados seletivamente sem prejudicar o funcionamento da lógica restante,

a qual esta em operação (execução). Estes dispositivos podem ser reconfigurados seletivamente enquanto estiverem ativos.

Para um FPGA ser reconfigurável dinamicamente, implica-se que deve ser capaz de se reconfigurar parcialmente enquanto ativo (energizado e em operação). Em nível de sistema, um módulo que contenha múltiplos FPGAs pode ser classificado como reconfigurável dinamicamente se os componentes FPGAs são reconfigurados individualmente [17].

Como os tempos de configuração não são desprezíveis, a habilidade de intercalar execução e reconfiguração, sem prejuízo do desempenho, é uma questão que ainda merece atenção e esforços de pesquisas [17].

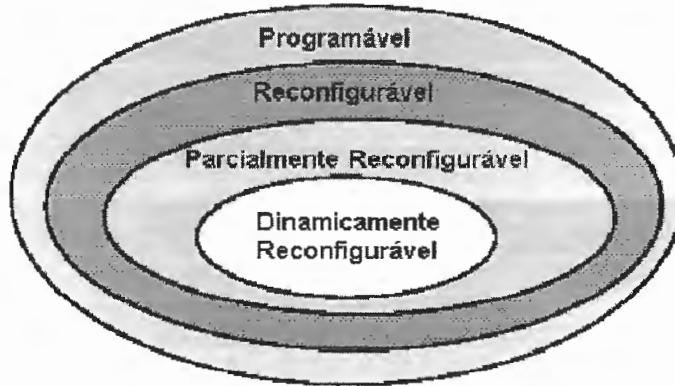

Um sistema de reconfiguração dinâmica inclui pelo menos uma área de reconfiguração onde blocos lógicos podem ser carregados em tempo de execução, como visto na Figura 3, que ilustra a reconfiguração dinâmica de um sistema composto de cinco circuitos ou tarefas, onde as tarefas de entrada e saída são permanentemente residentes no FPGA enquanto as três tarefas dinâmicas alternam-se sob o controle de um sinal de Swap [9].

Figura 3: Exemplo de Reconfiguração Dinâmica [10]

A capacidade de reconfiguração dinâmica permite o compartilhamento ao longo de tempo de tarefas diferentes, o que pode reduzir significativamente a área de silício exigida. Esta tecnologia torna possível o conceito de hardware ilimitado ou “Hardware Virtual” [15, 16].

A principal questão nesta abordagem é a implementação de um controlador capaz de manipular a reconfiguração de todas essas tarefas. Este controlador deve oferecer serviços como o carregamento e remoção de tarefas, escalonamento de tarefas e gerenciamento dos recursos.

Esta tecnologia vem desenvolvendo um novo conceito para circuitos integrados, chamado de S.O.C. (System On Chip), onde ela oferece uma nova opção com grande capacidade, velocidade e modularidade, para que os circuitos de hardware possam ser modificados em qualquer momento durante o seu uso.

Aliando-se ao conceito de modularidade dos FPGAs, o presente trabalho propõe um novo conceito de desenvolvimento de sistemas robóticos, o qual utilizará sistemas alternativos de hardware para a criação de novos robôs móveis, como:

- Utilizar sensores disponíveis no mercado ou mesmo implementar novos sensores com maior precisão;

- Agrupar sensores a um conjunto de hardware reconfigurável sem que haja restrição de fabricantes;

- Alcançar um patamar de desenvolvimento em nível de aplicação final, como desenvolver um robô que corta grama, realiza limpeza da casa entre outras tarefas, que possuem um certo grau de complexidade;

- Evoluir as características desses robôs sem a intervenção humana;

- Implementar um novo conceito de hardware para robôs utilizando hardware reconfigurável e F.P.G.As.

As possibilidades de expansão, utilizando esse novo paradigma, vão além das aplicações de navegação de robôs móveis existentes hoje. O trabalho proposto introduz um novo conceito de hardware para robôs móveis, onde todo o projeto de hardware poderá ser desenvolvido juntamente com o ambiente de programação e o simulador de hardware.

O sistema de desenvolvimento proposto é subdividido em duas partes, sendo elas:

- *Ambiente de Desenvolvimento*, interface de programação com o Usuário e desenvolvimento com a utilização das características do hardware específico;

- *Simulador de Aplicação*, que tem como objetivo simular as situações reais do ambiente utilizando a aplicação desenvolvida com hardware do robô.

Todo o projeto deve ser desenvolvido em um ambiente com todas as características dos componentes físicos, visando sempre manter a fidelidade das características dos mesmos, além de fornecer um ambiente amigável e de alto nível de programação, e implementação de novos componentes para sistemas robóticos.

Após toda a fase de projeto e desenvolvimento, este novo sistema deve ser validado em uma expansão do simulador Player/Stage, o qual deverá ter um módulo específico com todas as características apresentadas no ambiente de desenvolvimento.

### **Ambiente de Desenvolvimento e Programação**

Este ambiente é um ambiente de programação com uma linguagem desenvolvida para a simplificação das diretrizes utilizadas atualmente no desenvolvimento de sistemas de robôs móveis e baseada na linguagem GNU GCC.

Ele deverá ter como função principal a realização do processo de compilação e criação de um arquivo, o qual será executado no sistema operacional Embedded Linux [4] que é utilizado em sistemas embarcados. Além de prover um ambiente de programação para o hardware, ele também terá como objetivo gerar características que serão utilizadas no simulador para esse robô denominado Player/Stage [3], reproduzindo assim com a máxima fidelidade as características de hardware implementadas pelos fabricantes.

Com a incorporação dessa nova linguagem de programação ele também conseguirá implementar novas funcionalidades ao robô e seu simulador, como por exemplo, novos sensores, novos meios de mapeamento e novas funcionalidades que poderão ser melhoradas pelos desenvolvedores que utilizarão este sistema.

## Hardware reconfigurável do Robô

O ambiente de desenvolvimento de aplicações utiliza uma linguagem de alto nível para programação, sendo que o código produzido será transformado em um arquivo executável. Esse último será utilizado no sistema operacional embarcado  $\mu$ C Linux [5], que possuirá as bibliotecas com as descrições físicas dos hardwares auxiliares e trabalhará controlando também o funcionamento de todas as tarefas do hardware reconfigurável, implementado com FPGAs. Dessa forma conseguir-se-á uma independência do tipo de FPGA a ser utilizado no projeto.

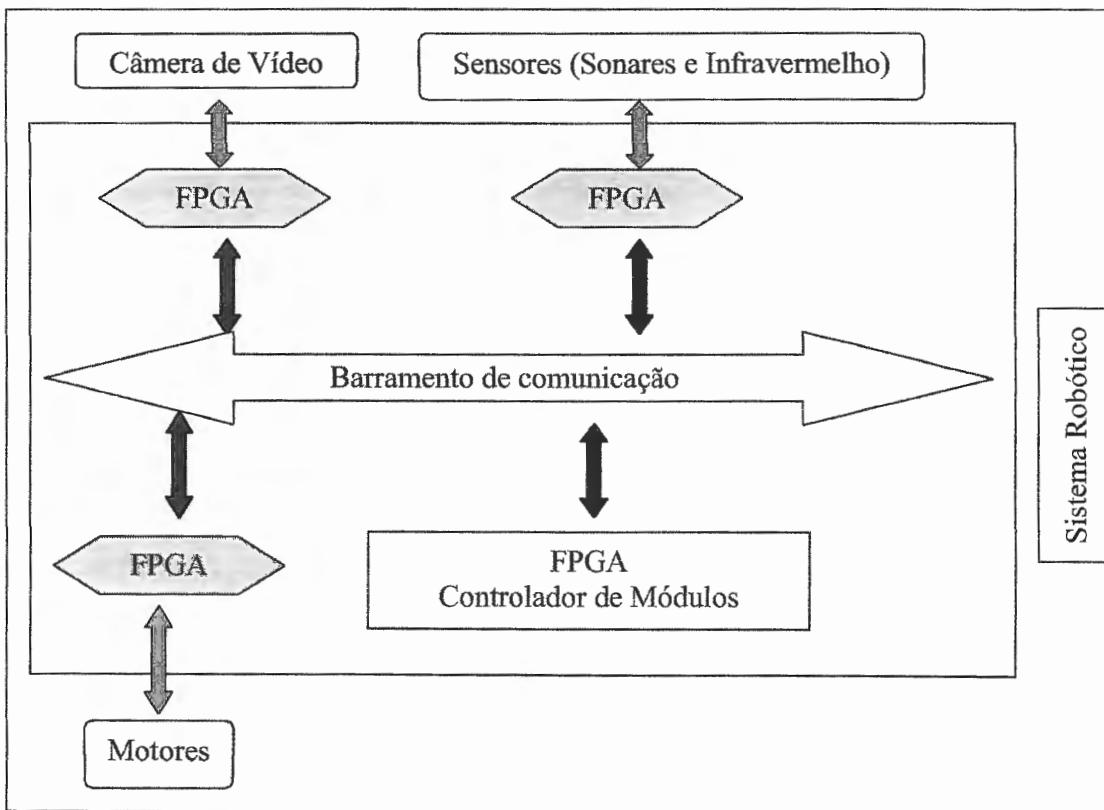

O sistema operacional é a interface de ligação entre o ambiente de desenvolvimento e o hardware propriamente dito. Contudo, para que esse S.O funcione corretamente é necessário adicionar todas as possíveis características do robô. Uma das estruturas analisadas inicialmente é a estrutura de um robô com diversas FPGA sendo que cada uma controlará uma função específica do robô, como por exemplo, uma FPGA responsável pelo controle dos motores de um robô, outra responsável pelo sensoriamento (sonares, infravermelhos e câmeras), entre outras tarefas. O sistema operacional constituirá então o núcleo de processamento de todas as tarefas do robô, decidindo o que e quando realizar uma tarefa, provendo com isso as mudanças de configuração do robô conforme a necessidade do sistema. A Figura 4 ilustra uma visão geral do sistema baseado em FPGAs.

Figura 4: Exemplo de Reconfiguração Dinâmica [10]

## **Simulador de Aplicações**

A função deste simulador é auxiliar o desenvolvedor do sistema robótico a validar seus aplicativos antes de implantá-los no hardware propriamente dito.

Este simulador comportará os dispositivos físicos do robô a ser implementado, isto quer dizer que, o simulador terá em sua implementação, uma cópia das características físicas, mecânicas e suas respectivas falhas (erros de leitura, erros de sincronização e falha em sensores) que os dispositivos possam apresentar.

A princípio, este simulador terá um driver (módulo) que estará acoplado no simulador Player/Stage [3], que é um software livre, e destina-se à simulação de ambientes para robôs móveis, sendo muito utilizado em diversas universidades ao redor do mundo .

## **Conclusão**

A intenção do projeto é criar um ambiente de desenvolvimento de aplicações para robôs móveis que utilizam arquitetura baseada em FPGAs. Os dispositivos utilizados em robôs móveis comerciais como, sensores, laser, etc., serão agregados a esse ambiente com a finalidade de prover uma interface de alto nível de desenvolvimento.

O projeto apresenta algumas dificuldades de implementação que são inerentes às ligações dos diversos sistemas e dispositivos em um único ambiente, sem que o programador desse ambiente perceba estas transições. Essas dificuldades são:

- Implementação de bibliotecas que controlem os dispositivos externos;

- Implementação de bibliotecas que realizam as tarefas de alto nível da linguagem de programação para os sistemas de robôs móveis;

- Integração do código gerado no ambiente de desenvolvimento e o sistema operacional que controla a FPGA;

- Integração do código gerado no ambiente de desenvolvimento com o simulador Player/Stage.

Devido a todos os aspectos já vistos, esse projeto é viabilizado pelo fato de que os sistemas reconfiguráveis estão cada vez mais presentes no mercado de hardware e, além disso, esse ambiente auxiliará a novos desenvolvedores criarem soluções aplicáveis à robótica sem que haja a necessidade da compreensão do funcionamento interno do hardware. Esse ambiente irá prover uma linguagem de alto nível para o desenvolvimento de aplicações em robótica, as quais funcionarão em uma arquitetura para propósito geral, reduzindo assim o valor final agregado a este robô e melhorando a aparência do sistema final.

## **Referências**

- [1] Scatena, Jean M., *Implementação de Mapas Topológicos para Navegação de Robôs Móveis baseadas em Computação Reconfigurável*, outubro de 2.002.

- [2] GNU GCC, Internet site address: <http://www.gnu.org> acessado em 16/09/2.004.

- [3] Player/Stage, Internet site address: <http://sourceforge.net/projects/playerstage/> acessado em 15/09/2.004.

- [4] Embedded Linux, Internet site address: <http://www.embedded-linux.org/> acessado em 01/09/2.004.

- [5] µC Linux, Internet site address: <http://www.uclinux.org/pub/uClinux/dist/> acessado em 10/09/2.004.

- [6] Aibo Sony, Internet site address: <http://www.sony.net/Products/aibo/> acessado em 16/09/2.004.

- [7] Altera Corporation, Internet address: <http://www.altera.com/products/devices/dev-index.jsp> acessado em 30/08/2.004.

- [8] Xilinx, Inc., The FPGA Virtex II Pro., Internet adress:: [http://www.xilinx.com/xlnx/xil\\_prodcat\\_landingpage.jsp?sGlobalNavPic=k=PRODUCTS](http://www.xilinx.com/xlnx/xil_prodcat_landingpage.jsp?sGlobalNavPic=k=PRODUCTS) acessado em 20/05/2.004.

- [9] Aragão, A. C. O. S., *Uma Arquitetura Reconfigurável Dinamicamente Dedicada ao Controle de Robôs Móveis*, ICMC USP. 2.000.

- [10] Aragão, A. C. O. S.; Marques, E., *A Tecnologia FPGA*, Relatório Técnico no. 60 – ICMC USP. Mar.2000.

- [11] Duckett T., Saffloti A., *Building Globally Consistent Gridmaps from Topologies*, Center for Applied Autonomous Sensor Systems Department of Technology, The University Örebro, SE-70182, Örebro, Sweden, 2.000.

- [12] Web Definitions, Internet address:

[http://www.hifn.com/support/Glossary\\_F.html](http://www.hifn.com/support/Glossary_F.html) acessado em 14/08/2004

- [13] Moreno J.M., Cabestany J., Cantó J. F., Insener J.M., *The Role of Dynamic Reconfiguration for Implementing Artificial Neural Networks Models in Programmable Hardware*, Dept. of Electronic Engineering, University of Catalunya, 2001.

- [14] Lysaght P., Dunlop J., *Dynamic ReconFiguration of Field Programmable Gate Arrays*, Department of Electronic and Electrical Engineering; University of Strathclyde, 1993.

- [15] Cardoso, J. M. P., Vestias M. P., *Architectures and Compilers to Support Reconfigurable Computing*, 1.999.

- [16] Haug, G., Rosenstiel W., 'Reconfigurable Hardware as Shared Resource for Parallel Threads', Proc. 5th Annual IEEE Symposium on Custom Computing Machines; IEEE Computer Society Press, p. 320 1997.

- [17] Wirthlin M. J., Hutchings B. L., 'A Dynamic Instruction Set Computer', in Proceedings of the 4th IEEE Symposium on FPGAs for Custom Computing Machines (FCCM'95), p. 99-107, April 19-21, 1995.