Received May 7, 2020, accepted June 1, 2020, date of publication August 3, 2020, date of current version August 18, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3014008

# A Comprehensive Non-Ideal Steady-State Analysis of a Threefold Operation Mode Interleaved-Based DC-DC Converter

RAFAEL FERNANDO QUIRINO MAGOSSI<sup>1</sup>, (Member, IEEE), DANIEL SILVA DE CASTRO<sup>1</sup>,

ANA LAÍS RUI OLIVEIRA<sup>2</sup>, AND

RICARDO QUADROS MACHADO<sup>1</sup>, (Senior Member, IEEE)

<sup>1</sup>Federal Center for Technological Education Celso Suckow da Fonseca, CEFET at Nova Friburgo, Nova Friburgo 28635-080, Brazil

<sup>2</sup>Department of Electrical and Computer Engineering, University of São Paulo, USP at São Carlos, São Carlos 13566-590, Brazil

Corresponding author: Rafael Fernando Quirino Magossi (rafael.magossi@cefet-rj.br)

This work was supported in part by the São Paulo Research Foundation (FAPESP) under Grant 2016/21120-2, Grant 2013/20721-4, Grant 2017/21577-5, and Grant 2016/25017-1 and in part by the Coordination for the Improvement of Higher Education Personnel (CAPES) under Grant 001 and Grant 88881.030370/2013-0.

**ABSTRACT** Formerly in the literature, a new interleaved-based boost converter was devised for multiple input voltage sources purposes. Nevertheless, when only a single input voltage source is connected to the 2-phase version of this converter, it can be seen as a compact interleaved boost with voltage multiplier (cIBVM). A brief description of cIBVM operation as well as the ideal modeling are already discussed in the literature for one specific range of duty-cycle. In this paper, we provide further analysis by considering the conduction and dynamic losses on the analytical model with a single voltage source. Moreover, we also obtained the analytical model considering the entire duty-cycle range showing that the converter can perform either a quadratic, a double or even a symmetric voltage gain depending solely on the switching strategy adopted. The analytical model was obtained using state-space representation and both its accuracy and the effectiveness of the results were validated from a Simulink-based cross validation and a complete sequence of experimental tests.

**INDEX TERMS** DC-DC converters, high step-up conversion ratio, multiple operation modes.

## I. INTRODUCTION

The DC-DC converters are devices that play a fundamental role in the proper operation of microgrids [1]–[3], electric vehicles [4], [5] and satellite applications [6], [7]. For this reason, many advanced studies that are entirely focused on either presenting a new topology or even better describing and exploring an existing topology in terms of modeling and non-ideal analyses have been appearing from the beginning of power electronics research [8], [9]. Within this frame of reference, it is important to state that the voltage gain and efficiency of the DC-DC converter under analysis are usually the performance relations that concentrate the most of the technological improvement effort and thus motivate the study [10].

Additionally, one of the most promising DC-DC converter topology reported in the literature is based on the

The associate editor coordinating the review of this manuscript and approving it for publication was Sze Sing Lee<sup>1</sup>.

well-known interleaved technique which ensures a large conversion ratio while providing high efficiency for components with reduced dimensions without compromising the DC-DC converter overall performance [11]–[13]. Moreover, interleaved-based DC-DC converters are more reliable when compared to non-interleaved types rated for the same power level owing to the increased number of power stages [14], reason why they are attractive for photovoltaic and fuel cells [15], [16].

The interleaved technique has been applied in many applications and can be used to supply voltage from low to medium/high power capabilities. In the low power end, for example, it has been seen the use of the interleaved technique in works such as [17], where the authors devised a converter rated for 7.7 W to be used in integrated circuits, and [18], where a step-down interleaved converter rated for 12.15 W was proposed for mobile low-power applications. Considering now the medium/high power end, other examples are the step-down interleaved converter rated for 500 W proposed

in [19] as well as the work presented in [20] where the authors devised a 30 kW step-up interleaved converter for hybrid electric vehicles applications.

Apart from that, the interleaved technique can also be combined with other design strategies as was shown in the high step-up interleaved converter proposed by [21] which explores coupled-inductor and switched-capacitor techniques to improve performance for distribution generation systems.

In this context, in [22] and [23] Gules, Pfitscher and Franco integrated the idea of voltage multiplier cells with the interleaved technique and devised a new DC-DC converter topology, which was named as interleaved boost with voltage multiplier (IBVM), that is capable of delivering a conversion ratio reasonably larger than that of the conventional interleaved boost. In this way, the IBVM became a very attractive DC-DC converter solution to high-power applications, although a complete description was still missing in the literature. For this reason, in [16] Fuzato and his colleagues elaborated a detailed work exploring the IBVM operation and non-ideal behavior from an extensive state-space model which enabled the authors to report more realistic static voltage gain and efficiency performances and also validate the modeling approach against a sequence of experimental results.

Following the same implementation concept, the DC-DC converter for multiple input voltage sources proposed in [24] by Zhou, Zhu and Luo can be seen as a reduced version of the IBVM, or else a compact IBVM (cIBVM). In terms of performance, the cIBVM develops the same conversion ratio, but on the other hand, in terms of topology it has the advantage of requiring three less components, thus being a better alternative to microgrid applications owing to the reduced manufacturing cost. In addition, cIBVM is an interleaved converter and it is naturally more reliable than single-phase converters.

For this reason, the cIBVM constitutes a more attractive DC-DC converter solution when compared to the conventional IBVM, and yet a complete description is not deeply explored in the literature, since the work initially presented by Zhou, Zhu and Luo addresses only an idealized modeling approach that does not provide a more complex and detailed evaluation of the non-ideal static voltage gain, the efficiency or even the effects of parasitic losses in the overall performance. Additionally, no analysis is given when the cIBVM is operating in a duty-cycle range lower than 50% ( $0 \leq K < 0.5$ ), that is, the authors limit the study for high duty-cycle ( $0.5 \leq K \leq 1$ ).

Differently from the study presented in [24], which is entirely based on ideal assumptions, in this paper we report a complete description of the 2-phase cIBVM operation and non-ideal behavior that is valid for both  $0 \leq K < 0.5$  and  $0.5 \leq K \leq 1$ , configuring operation modes 1 and 2, respectively. In addition, we lay aside the interleaved technique and go further to also analyze even a third operation mode (operation mode 3) which is obtained by simply changing the switching strategy to a complementary switching that is

valid for all  $K$ , in which case a different DC-DC converter with symmetric static voltage gain and high-efficiency is described.

The entire study is performed considering the three aforementioned operation modes which lead to three different non-ideal state-space models that include all the components parasitic conduction, switching and inductor core losses in continuous conduction mode (CCM). From these models, a detailed non-ideal analysis is performed to evaluate the parasitic resistive losses effects on the static voltage gain and the efficiency for each operation mode. The analytical model done is useful to design the converter. The accuracy of the obtained models and the effectiveness of the results are verified considering four test scenarios in which a Simulink-based cross validation and a complete sequence of experimental tests are performed.

In Section II, the ideal circuit description of the DC-DC converter presented in [24] and its basic operation are presented. The corresponding switching maps of both interleaved technique and complementary switching are given. In Section III, the non-ideal circuit description is presented and the state-space models of all feasible sub-circuits are obtained. In Section IV, these models are used to calculate the average models of the corresponding operation modes and in Section V an efficiency estimation is obtained based on conduction and dynamic power losses. A Simulink-based cross validation to verify the state-space models accuracy against a reference circuit is then presented in Section VI. In the sequence, a complete steady-state analysis in terms of static voltage gain is performed in Section VII. The experimental results are given in Section VIII. Finally, the conclusion of our work is presented in Section IX.

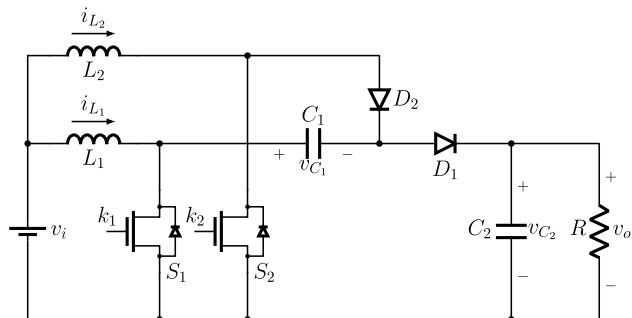

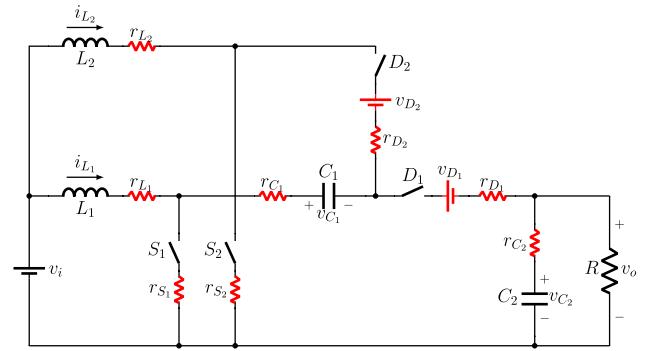

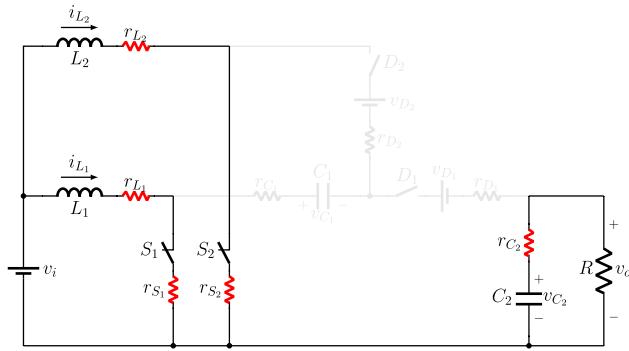

**FIGURE 1.** Compact IBVM proposed in [24].

## II. CIRCUIT DESCRIPTION AND OPERATION MODES

The converter topology evaluated in this paper is a compact solution of the IBVM converter as is shown in Fig. 1. Considering the same illustration and according to [24],  $i_{L1}$  and  $i_{L2}$  represent the currents flowing through the inductors,  $L_1$  and  $L_2$ ,  $v_{C1}$  and  $v_{C2}$  are the voltages on the capacitors,  $C_1$  and  $C_2$ ,  $v_i$  and  $v_o$  are the input and output voltages, and  $R$  is the equivalent load placed on the converter terminals, respectively.

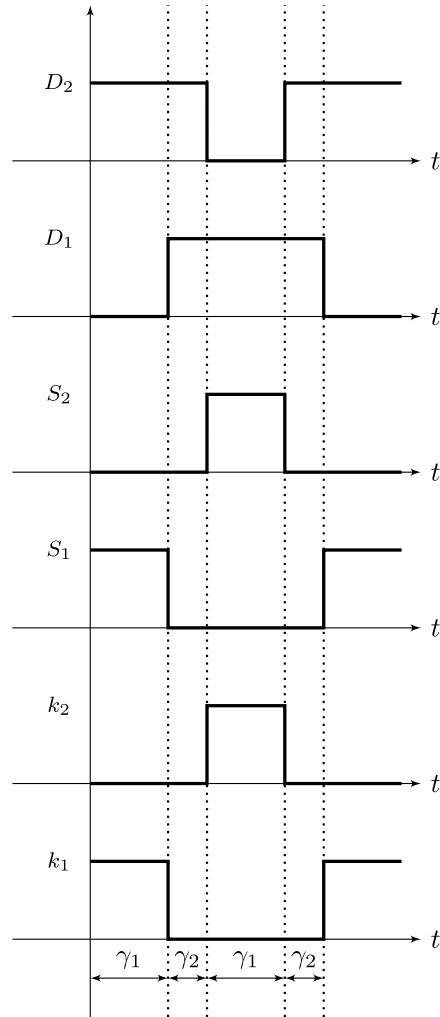

FIGURE 2. Switching map for  $0 \leq K < 0.5$ .

From Fig. 1, it can be noted that the cIBVM has a reduced number of components (semiconductors and storage devices), that is one capacitor and two diodes lesser than the conventional IBVM. Additionally, the topology requires four semiconductors, two controlled switches,  $S_1$  and  $S_2$ , activated by the driving signals  $k_1$  and  $k_2$ , and two diodes (non-active semiconductors),  $D_1$  and  $D_2$ , respectively.

#### A. INTERLEAVED TECHNIQUE

In this converter, the interleaved technique can be employed by generating  $k_1$  and  $k_2$  with  $180^\circ$  of displacement and applying the same duty-cycle at steady-state regime ( $K$ ) to both driving signals. Considering that the switching period is  $T_s$  and the switching frequency  $f_s = 1/T_s$ , let

$$\gamma_1 = KT_s, \quad \gamma_2 = \left(\frac{1}{2} - K\right)T_s, \\ \gamma_3 = \left(K - \frac{1}{2}\right)T_s \text{ and } \gamma_4 = (1 - K)T_s$$

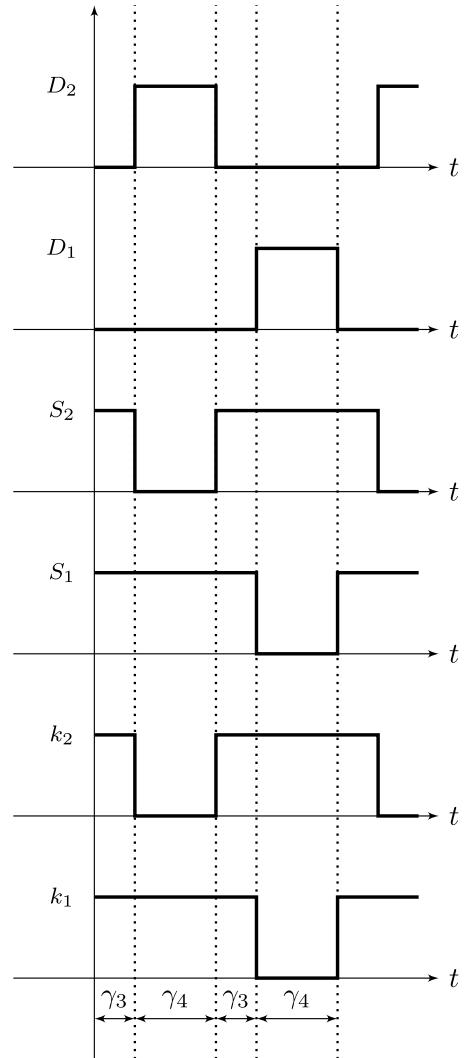

then, the switching maps for sub-intervals  $0 \leq K < 0.5$  and  $0.5 \leq K \leq 1$  are showed in Figs. 2 and 3, respectively.

FIGURE 3. Interleaved technique switching map for  $0.5 \leq K \leq 1$ .

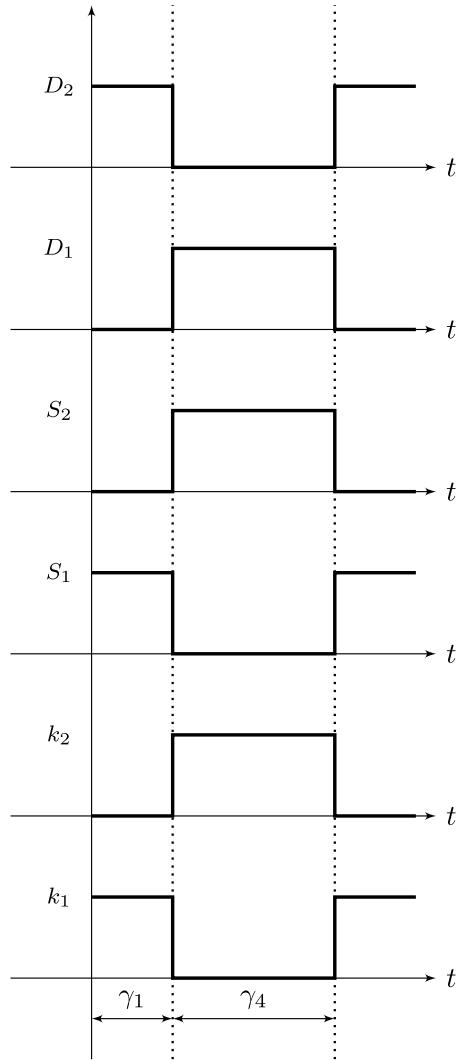

#### B. COMPLEMENTARY SWITCHING

In addition, the converter can also operate with the complementary switching. In this strategy, a duty-cycle  $K$  is applied to  $k_1$ , while the complement  $1 - K$  is used in  $k_2$ , thus producing the switching map illustrated in Fig. 4.

#### C. FINAL REMARKS FOR THE SWITCHING PATTERN

Based on the waveform pattern demonstrated in Figs. 2, 3 and 4, it is possible to conclude that the DC-DC converter analyzed in this paper can be completely described according to only four sub-circuits regardless the switching strategy that is used. That being said, Table 1 presents the switch configuration that must be observed to represent each possible sub-circuit.

Taking into account the aforementioned arguments, in the next section the state-space model related to each sub-circuit is obtained.

FIGURE 4. Switching map for the complementary operation mode.

TABLE 1. Switching pattern.

| Sub-circuit | $S_1$ | $S_2$ | $D_1$ | $D_2$ |

|-------------|-------|-------|-------|-------|

| 1           | OFF   | OFF   | ON    | ON    |

| 2           | ON    | OFF   | OFF   | ON    |

| 3           | OFF   | ON    | ON    | OFF   |

| 4           | ON    | ON    | OFF   | OFF   |

### III. STATE-SPACE MODELING APPROACH

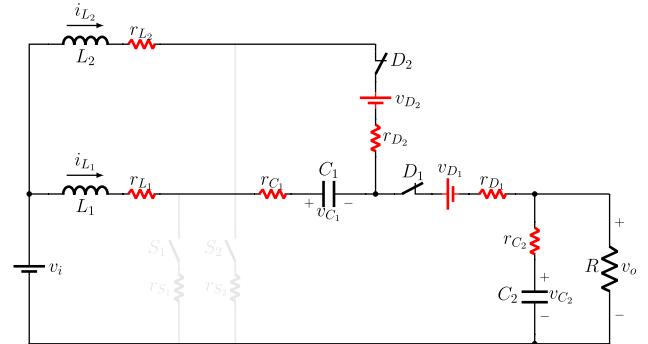

In order to analyze the converter efficiency as well as the non-ideal static voltage gain at steady-state regime, all the components parasitic conduction losses are included. Therefore, in the non-ideal circuit shown in Fig. 5,  $r_{L_1}$  and  $r_{L_2}$  are the conduction losses through inductors  $L_1$  and  $L_2$ ,  $r_{S_1}$ ,  $r_{S_2}$ ,  $r_{D_1}$  and  $r_{D_2}$  are the intrinsic resistances of semiconductors  $S_1$ ,  $S_2$ ,  $D_1$  and  $D_2$ , and  $r_{C_1}$  and  $r_{C_2}$  are the equivalent series resistances (ESR) in capacitors  $C_1$  and  $C_2$ , respectively. Moreover,  $v_{D_1}$  and  $v_{D_2}$  are the forward voltage drops in  $D_1$  and  $D_2$ , respectively.

FIGURE 5. Non-ideal clBVM converter.

In order to obtain the state-space representation for each possible sub-circuit in the next subsections, let us define the state vector ( $\mathbf{x}$ ), the input vector ( $\mathbf{u}$ ) and the output vector ( $\mathbf{y}$ ) as

$$\mathbf{x} = [i_{L_1} \quad i_{L_2} \quad v_{C_1} \quad v_{C_2}]^T, \quad \mathbf{u} = [v_i \quad v_{D_1} \quad v_{D_2}]^T, \quad y = v_o \text{ and } \dot{\mathbf{x}} = \frac{d\mathbf{x}}{dt}.$$

FIGURE 6. Sub-circuit 1.

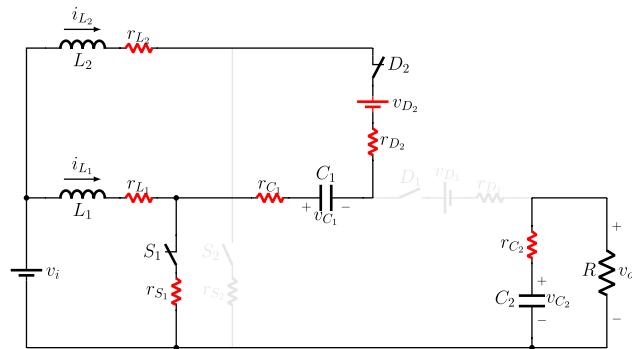

#### A. SUB-CIRCUIT 1

Applying the Kirchhoff's laws in the sub-circuit of Fig. 6, we obtain

$$\dot{\mathbf{x}} = \mathbf{A}_1 \mathbf{x} + \mathbf{B}_1 \mathbf{u} \text{ and} \\ y = \mathbf{E}_1 \mathbf{x},$$

where

$$\mathbf{A}_1 = \begin{bmatrix} a_{11} & a_{12} & a_{13} & a_{14} \\ a_{15} & a_{16} & a_{17} & a_{18} \\ a_{19} & a_{110} & a_{111} & a_{112} \\ a_{113} & a_{114} & a_{115} & a_{116} \end{bmatrix},$$

$$\mathbf{B}_1 = \begin{bmatrix} \frac{1}{L_1} & -\frac{1}{L_1} & 0 \\ \frac{1}{L_2} & -\frac{1}{L_2} & -\frac{1}{L_2} \\ 0 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix} \text{ and}$$

$$\mathbf{E}_1 = \begin{bmatrix} \frac{R r_{C_2}}{R + r_{C_2}} & \frac{R r_{C_2}}{R + r_{C_2}} & 0 & \frac{R}{R + r_{C_2}} \end{bmatrix}$$

with

$$a_{11} = \frac{R^2}{L_1 (R + r_{C_2})} - \frac{R + r_{C_1} + r_{D_1} + r_{L_1}}{L_1},$$

$$a_{12} = \frac{R^2}{L_1 (R + r_{C_2})} - \frac{R + r_{D_1}}{L_1},$$

$$a_{13} = -\frac{1}{L_1}, \quad a_{14} = -\frac{R}{L_1 (R + r_{C_2})},$$

$$a_{15} = \frac{R^2}{L_2 (R + r_{C_2})} - \frac{R + r_{D_1}}{L_2},$$

$$a_{16} = \frac{R^2}{L_2 (R + r_{C_2})} - \frac{R + r_{D_1} + r_{D_2} + r_{L_2}}{L_2},$$

$$a_{18} = -\frac{R}{L_2 (R + r_{C_2})}, \quad a_{19} = \frac{1}{C_1},$$

$$a_{13} = a_{14} = \frac{R}{C_2 (R + r_{C_2})}, \quad a_{16} = -\frac{1}{C_2 (R + r_{C_2})} \text{ and}$$

$$a_{17} = a_{10} = a_{11} = a_{12} = a_{15} = 0.$$

FIGURE 7. Sub-circuit 2.

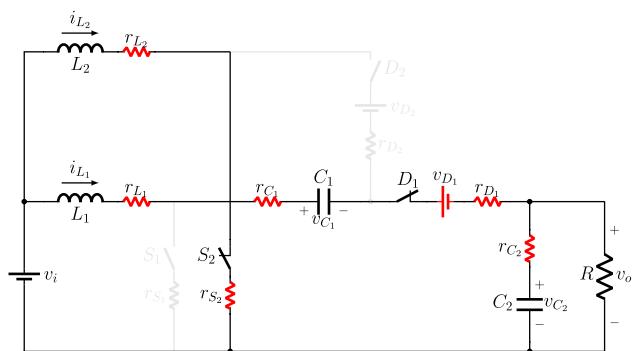

### B. SUB-CIRCUIT 2

Applying the Kirchhoff's laws in the sub-circuit of Fig. 7 yields to

$$\dot{x} = \mathbf{A}_2 x + \mathbf{B}_2 u \text{ and} \\ y = \mathbf{E}_2 x,$$

where

$$\mathbf{A}_2 = \begin{bmatrix} -\frac{r_{L_1} + r_{S_1}}{L_1} & -\frac{r_{S_1}}{L_1} & 0 & 0 \\ -\frac{r_{S_1}}{L_2} & a_{26} & \frac{1}{L_2} & 0 \\ 0 & -\frac{1}{C_1} & 0 & 0 \\ 0 & 0 & 0 & -\frac{1}{C_2 (R + r_{C_2})} \end{bmatrix},$$

$$\mathbf{B}_2 = \begin{bmatrix} \frac{1}{L_1} & 0 & 0 \\ \frac{1}{L_2} & 0 & -\frac{1}{L_2} \\ 0 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix} \text{ and} \\ \mathbf{E}_2 = \begin{bmatrix} 0 & 0 & 0 & \frac{R}{R + r_{C_2}} \end{bmatrix}.$$

with

$$a_{26} = -\frac{r_{C_1} + r_{D_2} + r_{L_2} + r_{S_1}}{L_2}.$$

FIGURE 8. Sub-circuit 3.

### C. SUB-CIRCUIT 3

In the third switching pattern, the corresponding sub-circuit is as illustrated in Fig. 8. Applying the Kirchhoff's laws results in

$$\dot{x} = \mathbf{A}_3 x + \mathbf{B}_3 u \text{ and}$$

$$y = \mathbf{E}_3 x,$$

where

$$\mathbf{A}_3 = \begin{bmatrix} a_{31} & 0 & -\frac{1}{L_1} & -\frac{R}{L_1 (R + r_{C_2})} \\ 0 & -\frac{r_{L_2} + r_{S_2}}{L_2} & 0 & 0 \\ \frac{1}{C_1} & 0 & 0 & 0 \\ \frac{R}{C_2 (R + r_{C_2})} & 0 & 0 & -\frac{1}{C_2 (R + r_{C_2})} \end{bmatrix},$$

$$\mathbf{B}_3 = \begin{bmatrix} \frac{1}{L_1} & -\frac{1}{L_1} & 0 \\ \frac{1}{L_2} & 0 & 0 \\ 0 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix} \text{ and} \\ \mathbf{E}_3 = \begin{bmatrix} \frac{R r_{C_2}}{R + r_{C_2}} & 0 & 0 & \frac{R}{R + r_{C_2}} \end{bmatrix}$$

with

$$a_{31} = \frac{R^2}{L_1 (R + r_{C_2})} - \frac{R + r_{C_1} + r_{D_1} + r_{L_1}}{L_1}.$$

FIGURE 9. Sub-circuit 4.

#### D. SUB-CIRCUIT 4

Finally, applying the Kirchhoff's laws in the sub-circuit shown in Fig. 9, we obtain as result

$$\begin{aligned}\dot{x} &= A_4 x + B_4 u \text{ and} \\ y &= E_4 x,\end{aligned}$$

where

$$\begin{aligned}A_4 &= \begin{bmatrix} -\frac{r_{L_1} + r_{S_1}}{L_1} & 0 & 0 & 0 \\ 0 & -\frac{r_{L_2} + r_{S_2}}{L_2} & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & -\frac{1}{C_2(R + r_{C_2})} \end{bmatrix}, \\ B_4 &= \begin{bmatrix} \frac{1}{L_1} & 0 & 0 \\ \frac{1}{L_2} & 0 & 0 \\ 0 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix} \text{ and} \\ E_4 &= \begin{bmatrix} 0 & 0 & 0 & \frac{R}{R + r_{C_2}} \end{bmatrix}.\end{aligned}$$

With the complete state-space model for each switching sub-interval, it is possible to calculate the average models to obtain the static voltage gain and the efficiency for all considered operation modes.

#### IV. AVERAGE VOLTAGE GAIN MODELING

The converter has 3 different operation modes, which are:

- 1) Interleaved switching for  $0 \leq K < 0.5$  (mode 1),

- 2) Interleaved switching for  $0.5 \leq K \leq 1$  (mode 2),

- 3) Complementary switching (mode 3).

Let  $q \in \{1, 2, 3\}$ . Assuming  $\bar{A}_q$ ,  $\bar{B}_q$  and  $\bar{E}_q$  as average state-space matrices, for a generic operation mode  $q$ , we have an algebraic system as

$$\begin{aligned}0 &= \bar{A}_q X + \bar{B}_q U \text{ and} \\ Y &= \bar{E}_q X\end{aligned}$$

such that the average value of the state variables ( $X$ ) and output ( $Y = V_o$ ), as a function of average value of the input

( $U = [V_i \ V_{D_1} \ V_{D_2}]^T$ ), are given by

$$X = -\bar{A}_q^{-1} \bar{B}_q U \text{ and} \quad (1)$$

$$Y = -\bar{E}_q \bar{A}_q^{-1} \bar{B}_q U. \quad (2)$$

Moreover, from (2), the static voltage gain ( $M_q$ ) can be calculated as

$$M_q =: \frac{V_o}{V_i} = -\bar{E}_q \bar{A}_q^{-1} \bar{B}_q U V_i^{-1} \quad (3)$$

and the ideal static voltage gain is obtained by setting

$$r_{L_1} = r_{L_2} = r_{C_1} = r_{C_2} = r_{D_1} = r_{D_2} = r_{S_1} = r_{S_2} = 0$$

and

$$V_{D_1} = V_{D_2} = 0$$

in (3).

#### A. MODE 1

For this operation mode, from Section II, we have

$$\begin{aligned}\bar{A}_1 &= A_1(1 - 2K) + A_2K + A_3K, \\ \bar{B}_1 &= B_1(1 - 2K) + B_2K + B_3K \text{ and} \\ \bar{E}_1 &= E_1(1 - 2K) + E_2K + E_3K.\end{aligned}$$

##### 1) NON-IDEAL GAIN

The ideal static voltage gain is

$$M_1 = \frac{m_{11}K^4 + m_{12}K^3 + m_{13}K^2 + m_{14}K + m_{15}}{m_{16}K^4 + m_{17}K^3 + m_{18}K^2 + m_{19}K + m_{10}} \quad (4)$$

where its coefficients are in Table 2.

##### 2) IDEAL GAIN

Considering null the losses, the ideal voltage gain is given by

$$M_1 = \frac{1}{(1 - K)^2},$$

i.e. the cIBVM converter operates with a quadratic voltage gain.

#### B. MODE 2

For this operation mode, from Section II, we have

$$\begin{aligned}\bar{A}_2 &= A_4(2K - 1) + A_2(1 - K) + A_3(1 - K), \\ \bar{B}_2 &= B_4(2K - 1) + B_2(1 - K) + B_3(1 - K) \text{ and} \\ \bar{E}_2 &= E_4(2K - 1) + E_2(1 - K) + E_3(1 - K).\end{aligned}$$

##### 1) NON-IDEAL GAIN

The non-ideal static voltage gain is

$$M_2 = \frac{m_{21}K^2 + m_{22}K + m_{23}}{m_{24}K^2 + m_{25}K + m_{26}} \quad (5)$$

and its coefficients are in Table 3.

**TABLE 2. Coefficients of (4).**

|           |                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $m_{11}$  | $-R^2 V_{D_1} - R^2 V_{D_2} - R r_{C_2} V_{D_1} - R r_{C_2} V_{D_2}$                                                                                                                                                                                                          |

| $m_{12}$  | $4 R^2 V_{D_1} + 4 R^2 V_{D_2} + 4 R r_{C_2} V_{D_1} + 4 R r_{C_2} V_{D_2}$                                                                                                                                                                                                   |

| $m_{13}$  | $R^2 V_i - 6 R^2 V_{D_2} - 6 R^2 V_{D_1} - 6 R r_{C_2} V_{D_1} - 6 R r_{C_2} V_{D_2} + R r_{C_2} V_i$                                                                                                                                                                         |

| $m_{14}$  | $4 R^2 V_{D_1} + 4 R^2 V_{D_2} - 2 R^2 V_i + 4 R r_{C_2} V_{D_1} + 4 R r_{C_2} V_{D_2} - 2 R r_{C_2} V_i$                                                                                                                                                                     |

| $m_{15}$  | $R^2 V_i - R^2 V_{D_2} - R^2 V_{D_1} - R r_{C_2} V_{D_1} - R r_{C_2} V_{D_2} + R r_{C_2} V_i$                                                                                                                                                                                 |

| $m_{16}$  | $R^2 V_i$                                                                                                                                                                                                                                                                     |

| $m_{17}$  | $R r_{C_2} V_i - 4 R^2 V_i + R r_{D_1} V_i - R r_{D_2} V_i + R r_{S_2} V_i + r_{C_2} r_{D_1} V_i - r_{C_2} r_{D_2} V_i + r_{C_2} r_{S_2} V_i$                                                                                                                                 |

| $m_{18}$  | $6 R^2 V_i - R r_{C_1} V_i + 3 R r_{D_2} V_i + R r_{L_1} V_i + R r_{L_2} V_i - 2 R r_{S_2} V_i - r_{C_1} r_{C_2} V_i + 3 r_{C_2} r_{D_2} V_i + r_{C_2} r_{L_1} V_i + r_{C_2} r_{L_2} V_i - 2 r_{C_2} r_{S_2} V_i$                                                             |

| $m_{19}$  | $R r_{C_1} V_i - 4 R^2 V_i - 2 R r_{C_2} V_i - 2 R r_{D_1} V_i - 3 R r_{D_2} V_i - 2 R r_{L_2} V_i + R r_{S_1} V_i + R r_{S_2} V_i + r_{C_1} r_{C_2} V_i - 2 r_{C_2} r_{D_1} V_i - 3 r_{C_2} r_{D_2} V_i - 2 r_{C_2} r_{L_2} V_i + r_{C_2} r_{S_1} V_i + r_{C_2} r_{S_2} V_i$ |

| $m_{110}$ | $R^2 V_i + R r_{C_2} V_i + R r_{D_1} V_i + R r_{D_2} V_i + R r_{L_2} V_i + r_{C_2} r_{D_1} V_i + r_{C_2} r_{D_2} V_i + r_{C_2} r_{L_2} V_i$                                                                                                                                   |

**TABLE 3. Coefficients of (5).**

|          |                                                                                                                                                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $m_{21}$ | $-R^2 V_{D_1} - R^2 V_{D_2} - R r_{C_2} V_{D_1} - R r_{C_2} V_{D_2}$                                                                                                                                                                                                  |

| $m_{22}$ | $2 R^2 V_{D_1} + 2 R^2 V_{D_2} - 2 R^2 V_i + 2 R r_{C_2} V_{D_1} + 2 R r_{C_2} V_{D_2} - 2 R r_{C_2} V_i$                                                                                                                                                             |

| $m_{23}$ | $2 R^2 V_i - R^2 V_{D_2} - R^2 V_{D_1} - R r_{C_2} V_{D_1} - R r_{C_2} V_{D_2} + 2 R r_{C_2} V_i$                                                                                                                                                                     |

| $m_{24}$ | $R^2 V_i$                                                                                                                                                                                                                                                             |

| $m_{25}$ | $R r_{S_2} V_i - 2 R r_{C_1} V_i - R r_{C_2} V_i - R r_{D_1} V_i - R r_{D_2} V_i - 2 R r_{S_1} V_i - 2 R^2 V_i - 2 r_{C_1} r_{C_2} V_i - r_{C_2} r_{D_1} V_i - r_{C_2} r_{D_2} V_i - 2 r_{C_2} r_{S_1} V_i + r_{C_2} r_{S_2} V_i$                                     |

| $m_{26}$ | $R^2 V_i + 2 R r_{C_1} V_i + R r_{C_2} V_i + R r_{D_1} V_i + R r_{D_2} V_i + R r_{L_1} V_i + R r_{L_2} V_i + 3 R r_{S_1} V_i + 2 r_{C_1} r_{C_2} V_i + r_{C_2} r_{D_1} V_i + r_{C_2} r_{D_2} V_i + r_{C_2} r_{L_1} V_i + r_{C_2} r_{L_2} V_i + 3 r_{C_2} r_{S_1} V_i$ |

## 2) IDEAL GAIN

The ideal voltage gain is given by

$$M_2 = \frac{2}{(1 - K)},$$

i.e. the cIBVM converter has double voltage gain as the classical IBVM converter.

## C. MODE 3

In this case, from Section II, we have

$$\begin{aligned} \bar{\mathbf{A}}_3 &= \mathbf{A}_2 K + \mathbf{A}_3 (1 - K), \\ \bar{\mathbf{B}}_3 &= \mathbf{B}_2 K + \mathbf{B}_3 (1 - K) \text{ and} \\ \bar{\mathbf{E}}_3 &= \mathbf{E}_2 K + \mathbf{E}_3 (1 - K). \end{aligned}$$

### 1) NON-IDEAL GAIN

The ideal static voltage gain is

$$M_3 = \frac{m_{31} K^4 + m_{32} K^3 + m_{33} K^2 + m_{34} K}{m_{35} K^4 + m_{36} K^3 + m_{37} K^2 + m_{38} K + m_{39}} \quad (6)$$

and its coefficients are in Table 4.

**TABLE 4. Coefficients of (6).**

|          |                                                                                                                                                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $m_{31}$ | $-\bar{R}^2 V_{D_1} - \bar{R}^2 V_{D_2} - R r_{C_2} V_{D_1} - R r_{C_2} V_{D_2}$                                                                                                                                                                                      |

| $m_{32}$ | $2 \bar{R}^2 V_{D_1} + 2 \bar{R}^2 V_{D_2} + 2 R r_{C_2} V_{D_1} + 2 R r_{C_2} V_{D_2}$                                                                                                                                                                               |

| $m_{33}$ | $-\bar{R}^2 V_{D_1} - \bar{R}^2 V_{D_2} - R^2 V_i - R r_{C_2} V_{D_1} - R r_{C_2} V_{D_2} - R r_{C_2} V_i$                                                                                                                                                            |

| $m_{34}$ | $V_i \bar{R}^2 + r_{C_2} V_i R$                                                                                                                                                                                                                                       |

| $m_{35}$ | $R^2 V_i$                                                                                                                                                                                                                                                             |

| $m_{36}$ | $R r_{D_2} V_i - R r_{C_2} V_i - R r_{D_1} V_i - 2 R^2 V_i - R r_{S_2} V_i - r_{C_2} r_{D_1} V_i + r_{C_2} r_{D_2} V_i - r_{C_2} r_{S_2} V_i$                                                                                                                         |

| $m_{37}$ | $R^2 V_i - R r_{C_1} V_i + R r_{C_2} V_i + R r_{D_1} V_i - 2 R r_{D_2} V_i + R r_{L_1} V_i + R r_{L_2} V_i + 3 R r_{S_2} V_i - r_{C_1} r_{C_2} V_i + r_{C_2} r_{D_1} V_i - 2 r_{C_2} r_{D_2} V_i + r_{C_2} r_{L_1} V_i + r_{C_2} r_{L_2} V_i + 3 r_{C_2} r_{S_2} V_i$ |

| $m_{38}$ | $R r_{C_1} V_i + R r_{D_2} V_i - 2 R r_{L_2} V_i + R r_{S_1} V_i - 3 R r_{S_2} V_i + r_{C_1} r_{C_2} V_i + r_{C_2} r_{D_2} V_i - 2 r_{C_2} r_{L_2} V_i + r_{C_2} r_{S_1} V_i - 3 r_{C_2} r_{S_2} V_i$                                                                 |

| $m_{39}$ | $R r_{L_2} V_i + R r_{S_2} V_i + r_{C_2} r_{L_2} V_i + r_{C_2} r_{S_2} V_i$                                                                                                                                                                                           |

### 2) IDEAL GAIN

The ideal voltage gain is given by

$$M_3 = \frac{1}{K(1 - K)}.$$

In this operation mode, it is easy to observe that the converter has a symmetric voltage gain, i.e. high gain at low and high values of duty-cycle.

## V. EFFICIENCY ESTIMATION

Unlike was done to obtain an explicit analytical solution for the average voltage gain, the explicit analytical solution for efficiency is not suitable to be displayed, since it results in a rational function with extensive coefficients. Nevertheless, the efficiency can be defined and then evaluated numerically as in [19], [21].

In this section, the efficiency efficiency of the converter is defined considering conduction, switching and inductor

core losses, i.e. the efficiency in any operation mode is rated as a function of power input, power output and the power losses.

#### A. INPUT POWER

Let  $i_i$  be the input current. Then,  $i_i$  is given by

$$i_i = i_{L_1} + i_{L_2}. \quad (7)$$

Assuming  $v_i = V_i$  as constant, the input power in steady-state is written as

$$P_i = \lim_{t \rightarrow \infty} \frac{1}{T_s} \int_t^{t+T_s} V_i i_i dt = V_i I_i \quad (8)$$

where  $I_i$  the average current of the input voltage source. Then, let  $\mathbf{J} = [1 \ 1 \ 0 \ 0]$ , for any operation mode,  $I_i$  can be expressed as

$$I_i = \mathbf{J} \mathbf{X}, \quad (9)$$

which leads to

$$I_i = I_{L_1} + I_{L_2}, \quad (10)$$

where  $I_{L_1}$  and  $I_{L_2}$  are the average currents flowing through inductors  $L_1$  and  $L_2$ , respectively. Therefore,

$$P_i = V_i \mathbf{J} \mathbf{X}. \quad (11)$$

#### B. LOAD POWER

For a constant load  $R$ , the instantaneous load power ( $p_R$ ) is given by

$$p_R = \frac{v_o^2}{R} \quad (12)$$

then, the load power consumption in steady-state is given by

$$P_R = \lim_{t \rightarrow \infty} \frac{1}{RT_s} \int_t^{t+T_s} v_o^2 dt$$

yielding to

$$P_R = \frac{V_{o_{rms}}^2}{R} \quad (13)$$

where

$$V_{o_{rms}} = \lim_{t \rightarrow \infty} \sqrt{\frac{1}{T_s} \int_t^{t+T_s} v_o^2 dt}.$$

Moreover, assuming the  $C_2$  large enough,  $V_{o_{rms}} \rightarrow V_o$  and

$$P_R = \frac{V_o^2}{R}, \quad (14)$$

which simplifies the efficiency estimation.

#### C. POWER LOSSES

The most relevant power losses can be separated as conduction and dynamic losses, where the last is essentially composed by switching and inductor core losses.

The conduction power loss is obtained by the power dissipated through the conduction parasitic resistances of the devices as well as the diodes forward voltage drops. The dynamic power loss depends on the switching frequency and is equal to the sum of power losses by virtue of switching transition and inductor core. The switching power losses occur during semiconductors transitions and is present in active switches and diodes [25].

Note that the load power already computes the device's conduction power losses which include the power dissipated as a result of the direct voltage drops of the diodes and the resistances of the switches and storage devices. However, it must be said that the dynamic power loss is relevant for efficiency analyses and therefore must be considered [19], [21], [26], [27]. Next we breakdown the power losses derivation.

##### 1) CONDUCTION POWER LOSS

The conduction power loss ( $P_\tau$ ) portion for any operation mode is straightforward to be obtained in our modeling and it is given by

$$P_\tau \triangleq P_i - P_R.$$

Next we estimate the switching power losses.

##### 2) SWITCHING POWER LOSSES

The estimation of the switching losses on the active semiconductors and diodes can be performed as shown in [25], [28]. In this case, we consider the turn-off loss on the diodes, the rise/fall time, and the output capacitance on active switches.

Let  $t_{r1}$  and  $t_{r2}$  be the rise time,  $t_{f1}$  and  $t_{f2}$  be the fall time of the semiconductors  $S_1$  and  $S_2$ , and  $Q_{r1}$  and  $Q_{r2}$  represent the reverse recovery charge of the diodes  $D_1$  and  $D_2$ , respectively.

Additionally,  $V_{C_1}$  is the average voltage on  $C_1$ , while  $P_{swD_1}$ ,  $P_{swD_2}$ ,  $P_{swS_1}$  and  $P_{swS_2}$  are the switching losses through  $D_1$ ,  $D_2$ ,  $S_1$  and  $S_2$ , respectively.

The switching power losses are estimated by

$$\begin{aligned} P_{swD_1} &= |\Phi_1| Q_{r1} f_s, \\ P_{swD_2} &= |\Phi_2| Q_{r2} f_s, \\ P_{swS_1} &= \frac{1}{2} (t_{r1} + t_{f1}) |\Phi_3| f_s, \\ P_{swS_2} &= \frac{1}{2} (t_{r2} + t_{f2}) |\Phi_4| f_s \end{aligned}$$

where  $\Phi_1$ ,  $\Phi_2$ ,  $\Phi_3$ ,  $\Phi_4$ ,  $\Phi_5$  and  $\Phi_6$  are given in Table 5 for each operation mode.

*Remark 1:* Let  $C_{oss1}$  and  $C_{oss2}$  be the output capacitance of switches  $S_1$  and  $S_2$ . Accordingly with [29], the power loss due

**TABLE 5.** Coefficients  $\Phi_1$ ,  $\Phi_2$ ,  $\Phi_3$  and  $\Phi_4$  for switching power loss estimation of each operation mode.

|          | Mode 1                               | Mode 2                       | Mode 3                               |

|----------|--------------------------------------|------------------------------|--------------------------------------|

| $\Phi_1$ | $V_o + V_{C_1}$                      | $V_o + V_{C_1}$              | $V_o + V_{C_1}$                      |

| $\Phi_2$ | $V_o$                                | $V_o + V_{C_1}$              | $V_o$                                |

| $\Phi_3$ | $(V_o + V_{C_1})(I_{L_1} + I_{L_2})$ | $V_{C_1}(I_{L_1} + I_{L_2})$ | $(V_o + V_{C_1})(I_{L_1} + I_{L_2})$ |

| $\Phi_4$ | $V_o I_{L_2}$                        | $(V_o + V_{C_1}) I_{L_2}$    | $V_{C_1} I_{L_2}$                    |

$C_{oss_1}$  and  $C_{oss_2}$  is already computed in the parameters  $P_{sws_1}$  and  $P_{sws_2}$ .

Let  $P_{ISS_1}$  and  $P_{ISS_2}$  be the power losses in the switch gate,  $Q_{g_1}$  and  $Q_{g_2}$  be the total gate charge and  $V_{C_{G_1}}$  and  $V_{C_{G_2}}$  represent the supply voltage of gate control circuit of  $S_1$  and  $S_2$ , respectively, then

$$P_{ISS_1} = Q_{g_1} V_{C_{G_1}} f_s,$$

$$P_{ISS_2} = Q_{g_2} V_{C_{G_2}} f_s.$$

### 3) CORE INDUCTOR POWER LOSS

The major contribution of the inductor core losses are by virtue of hysteresis and eddy current. Let  $P_{swL_1}$  and  $P_{swL_2}$  be the inductor core loss through  $L_1$  and  $L_2$ , respectively, then accordingly with [25], the inductor core power loss may be estimated by the Steinmetz's equation

$$P_{swL_1} = \lambda_1 f_s^{\alpha_1} \Delta B_1^{\beta_1} \hat{v}_1,$$

$$P_{swL_2} = \lambda_2 f_s^{\alpha_2} \Delta B_2^{\beta_2} \hat{v}_2,$$

where  $\hat{v}_1$ ,  $\hat{v}_2$  are the volume of the inductor core,  $\lambda_1$ ,  $\lambda_2$ ,  $\alpha_1$ ,  $\alpha_2$ ,  $\beta_1$  and  $\beta_2$  are constant depending on the core material which can be found in technical specifications of core manufacturers, and  $\Delta B_1$ ,  $\Delta B_2$  are the maximum induction on core given by

$$\Delta B_1 = \frac{\Delta i_{L_1} L_1}{2 \hat{S}_1 N_1}, \quad \Delta B_2 = \frac{\Delta i_{L_2} L_2}{2 \hat{S}_2 N_2}$$

where  $\Delta i_{L_1}$  and  $\Delta i_{L_2}$  are the change in inductor current,  $\hat{S}_1$  and  $\hat{S}_2$  are the cross-section area, and  $N_1$  and  $N_2$  are the number of turns in  $L_1$  and  $L_2$ , respectively [25].

### 4) DYNAMIC POWER LOSS

The total dynamic power loss ( $P_v$ ) is calculated as the sum of the switching power losses and is obtained by doing

$$P_v \triangleq P_{swD_1} + P_{swD_2} + P_{sws_1} + P_{sws_2} + P_{swL_1} + P_{swL_2} + P_{ISS_1} + P_{ISS_2} \quad (15)$$

### D. OUTPUT POWER

The output power ( $P_o$ ) is thus given by

$$P_o = P_i - P_\tau - P_v$$

and the efficiency is estimated by

$$\eta = \frac{P_o}{P_i}. \quad (16)$$

Note that as the output power depends on the power losses, which are different for each operation mode, then the efficiency depends on the operation mode. In the next section we perform a simulation to validate the modeling approach.

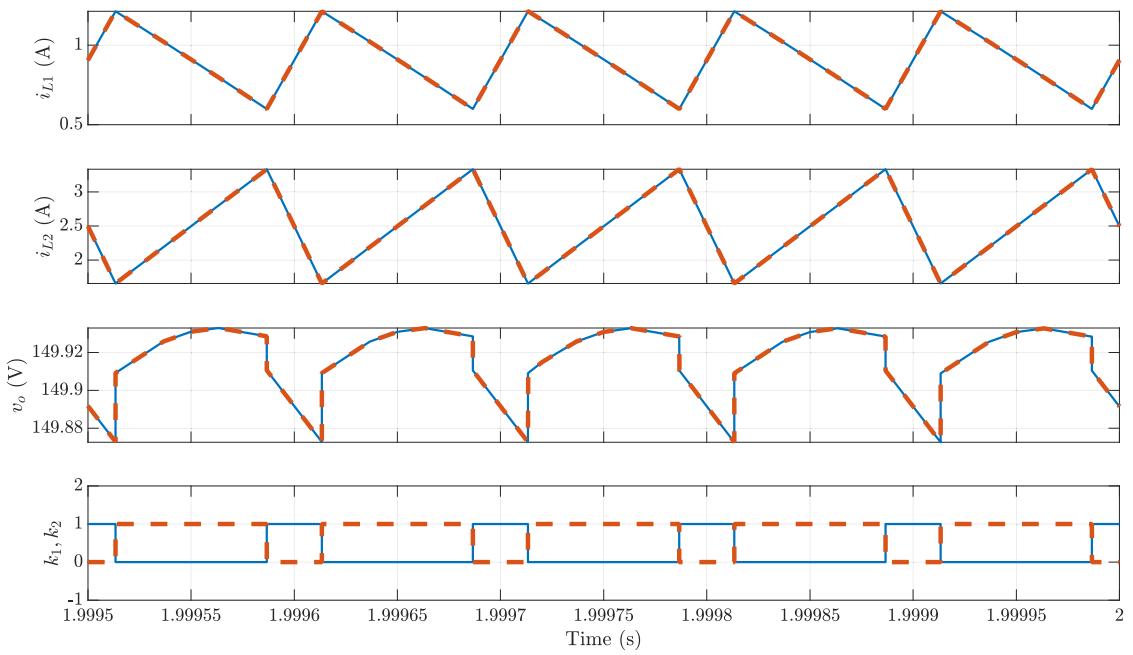

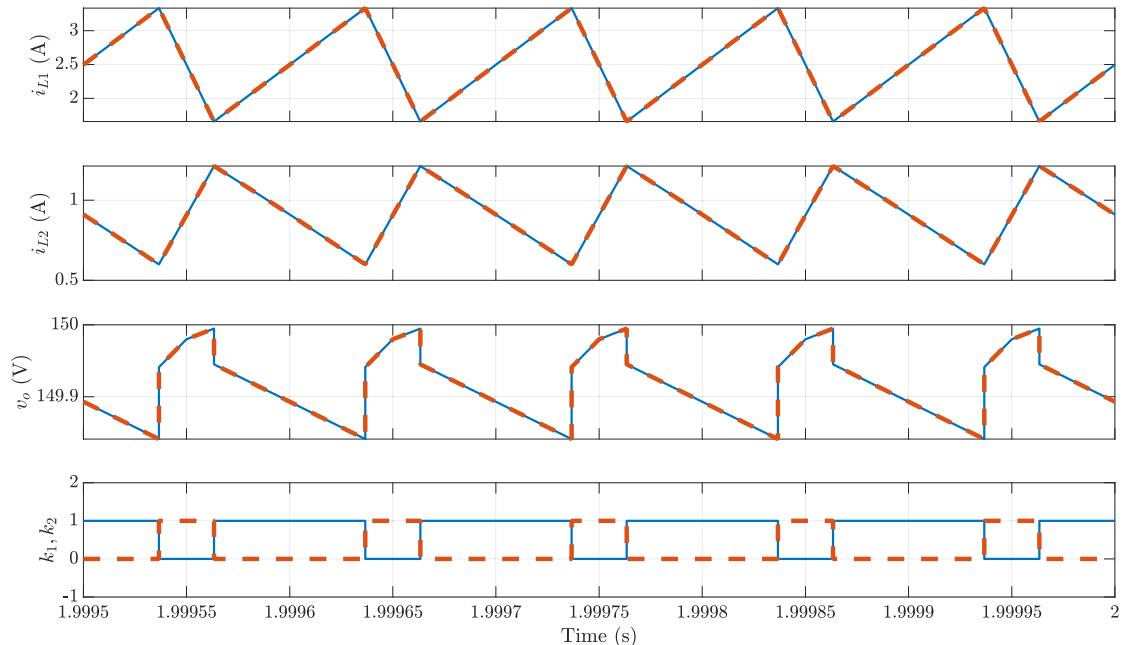

## VI. SWITCHED MODEL VALIDATION

To validate the cIBVM models, a set of time-domain simulations are performed in which the switched model responses are compared to those of the switched circuit assembled in the Matlab/Simulink environment. In the analysis, we evaluated the interleaved and the complementary operation modes by observing states  $i_{L_1}$  and  $i_{L_2}$ , the cIBVM terminal voltage  $v_o$ , and the duty-cycles  $k_1$  and  $k_2$ , respectively.

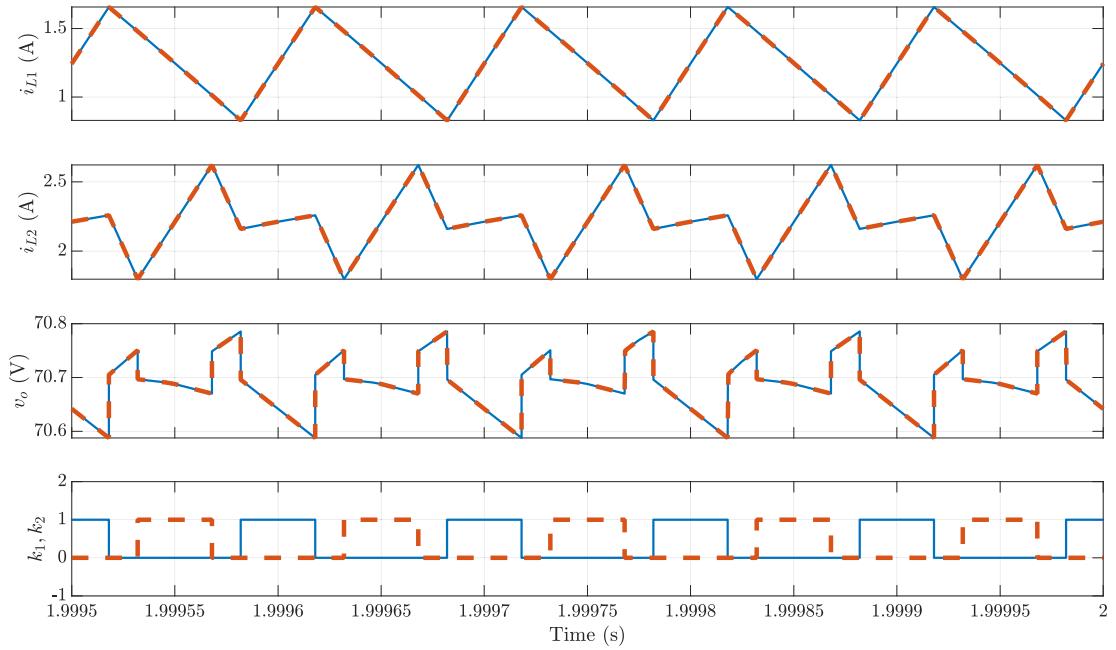

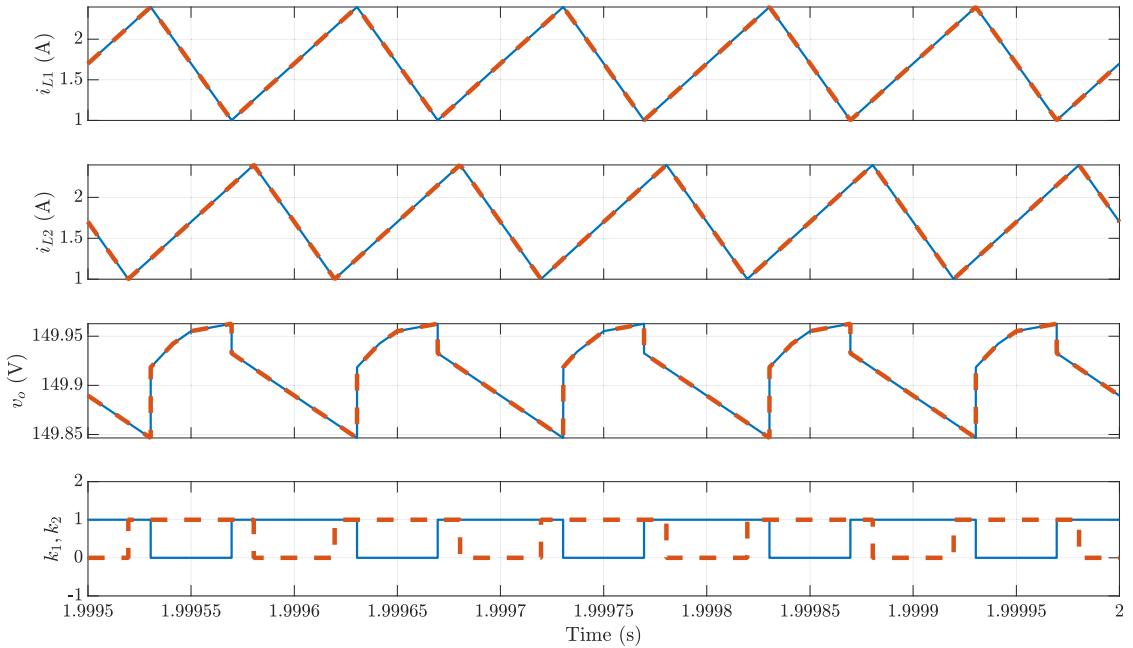

In this context, four different scenarios are considered in order to evaluate the cIBVM converter performance when it is processing approximately 100 W. In Table 8, the scenarios are given in terms of the corresponding operation mode, duty-cycle at steady-state regime, and 100 W resistance load value. The considered nominal parameters of the converter are rated in Table 6. As for the dynamic power loss estimation, the parameters that were used are given in Table 7.

**TABLE 6.** Nominal parameters.

| Parameter | Value          | Parameter | Value       |

|-----------|----------------|-----------|-------------|

| $r_{L_1}$ | 98 m $\Omega$  | $L_1$     | 1.3 mH      |

| $r_{L_2}$ | 98 m $\Omega$  | $L_2$     | 1.3 mH      |

| $r_{C_1}$ | 25 m $\Omega$  | $C_1$     | 100 $\mu$ F |

| $r_{C_2}$ | 30 m $\Omega$  | $C_2$     | 470 $\mu$ F |

| $r_{S_1}$ | 8 m $\Omega$   | $f_s$     | 10 kHz      |

| $r_{S_2}$ | 8 m $\Omega$   | $v_i$     | 30 V        |

| $r_{D_1}$ | 7.1 m $\Omega$ | $V_{D_1}$ | 1.01 V      |

| $r_{D_2}$ | 7.1 m $\Omega$ | $V_{D_2}$ | 1.01 V      |

The steady-state condition of the scenarios in Table 8 are shown in Figs. 11, 12, 13 and 14, respectively. As can be seen, the results show that the analytical models derived in this paper match precisely with the switched circuit.

In Table 9, the average currents ( $I_{L_1}$  and  $I_{L_2}$ ) and voltages ( $V_o$  and  $V_i$ ) are evaluated, while in Table 10 the analyzes are performed in terms of the input and output

**TABLE 7.** Parameters for dynamic power losses estimation.

| Parameter                  | Value               | Parameter              | Value             |

|----------------------------|---------------------|------------------------|-------------------|

| $Q_{r_1}, Q_{r_2}$         | $0.9 \mu\text{C}$   | $t_{r_1}, t_{r_2}$     | 105 ns            |

| $t_{f_1}, t_{f_2}$         | 74 ns               | $\lambda_1, \lambda_2$ | 17.26             |

| $N_1, N_2$                 | 150                 | $\hat{S}_1, \hat{S}_2$ | 6 cm <sup>2</sup> |

| $\alpha_1, \alpha_2$       | 1.31                | $\beta_1, \beta_2$     | 2.9               |

| $\hat{v}_1, \hat{v}_2$     | 151 cm <sup>3</sup> | $Q_{g_1}, Q_{g_2}$     | 161 nC            |

| $V_{C_{G_1}}, V_{C_{G_2}}$ | 15 V                | —                      | —                 |

**TABLE 8.** Test scenarios.

| Scenario | Mode | $K$    | $R (\Omega)$ |

|----------|------|--------|--------------|

| 1        | 1    | 0.3604 | 50           |

| 2        | 2    | 0.6080 | 225          |

| 3        | 3    | 0.2670 | 225          |

| 4        | 3    | 0.7331 | 225          |

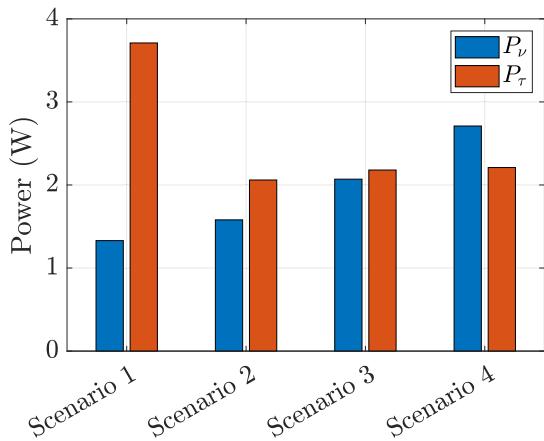

**FIGURE 10.** Power losses breakdown of simulated scenarios. The blue bar is the dynamic power loss and the red bar the conduction power loss.**TABLE 9.** Average values of the state currents, input and output voltages - simulated scenarios.

| Scenario | $I_{L_1}$ (A) | $I_{L_2}$ (A) | $V_o$ | $V_i$ |

|----------|---------------|---------------|-------|-------|

| 1        | 1.24          | 2.21          | 70.7  | 30.00 |

| 2        | 1.70          | 1.70          | 149.9 | 30.00 |

| 3        | 0.91          | 2.49          | 149.9 | 30.00 |

| 4        | 2.49          | 0.91          | 149.9 | 30.00 |

powers ( $P_i$  and  $P_o$ ), the voltage gain and the converter efficiency. In addition, the power losses breakdown is shown in Fig. 10.

From Fig. 10, it is possible to conclude that the conduction power loss ( $P_\tau$ ) is dominant in scenarios 1 and 2, equivalent to dynamic power loss ( $P_v$ ) in scenario 3 and lightly inferior in scenario 4, respectively.

**TABLE 10.** Voltage gain and efficiency-simulated scenarios.

| Scenario | $P_i$ (W) | $P_o$ (W) | Voltage Gain | $\eta$ (%) |

|----------|-----------|-----------|--------------|------------|

| 1        | 103.71    | 98.27     | 2.35         | 94.75      |

| 2        | 102.06    | 98.42     | 5.00         | 96.43      |

| 3        | 102.17    | 97.92     | 5.00         | 95.83      |

| 4        | 102.22    | 97.28     | 5.00         | 95.17      |

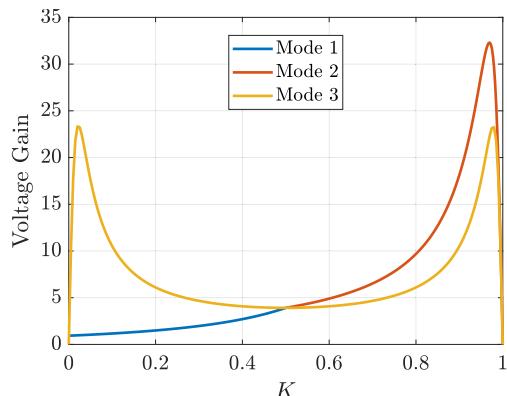

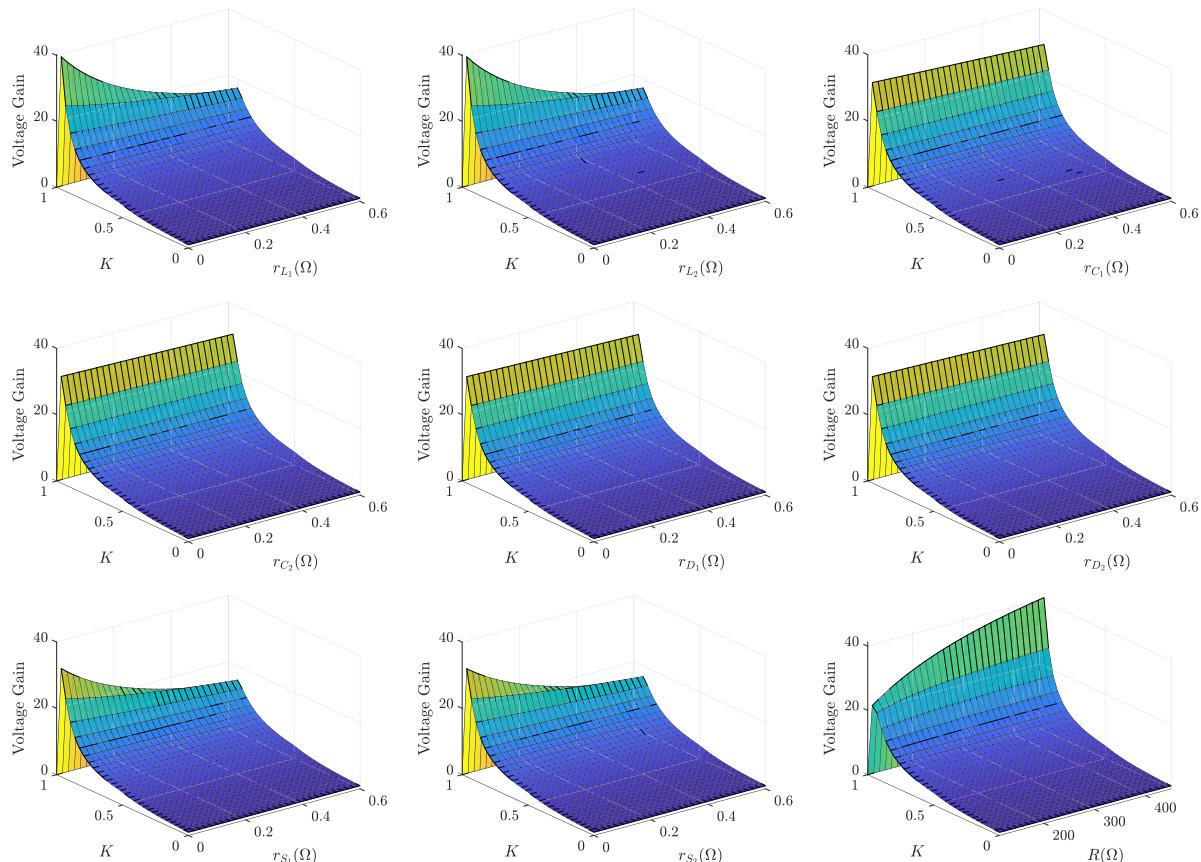

## VII. RESISTIVE LOSSES EFFECT ON THE VOLTAGE GAIN

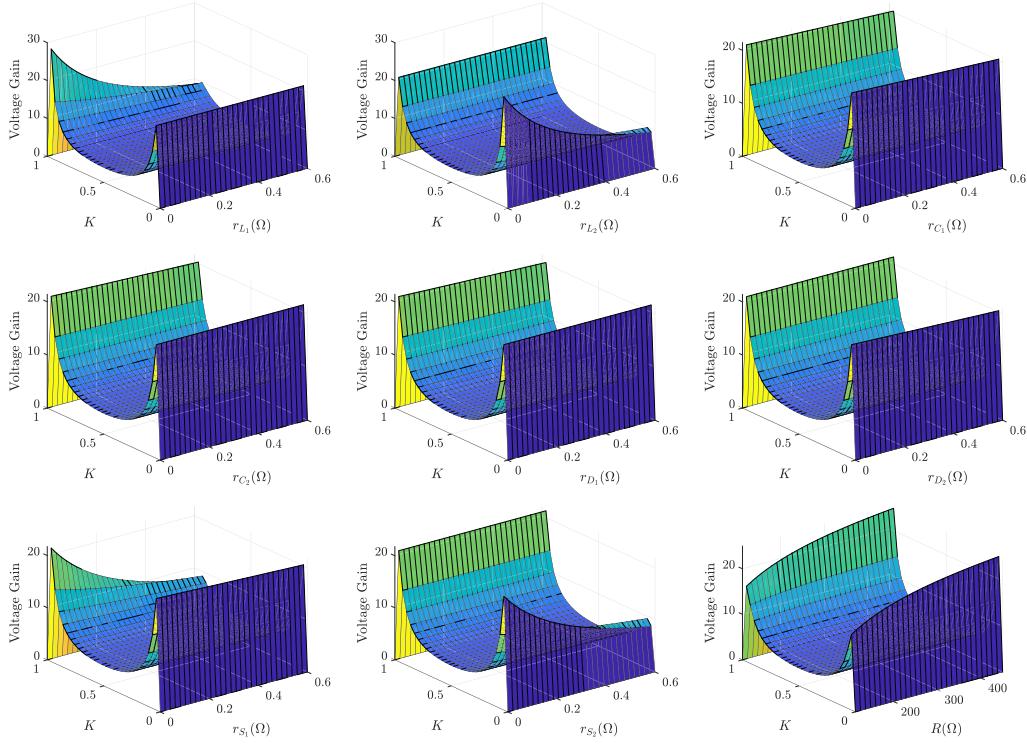

A set of waveforms were computed for each operation mode to evaluate the effects of the duty-cycle at steady-state regime ( $K$ ), the parasitic resistances and load demanded on the voltage gain. To perform the tests, we considered  $R = 225 \Omega$  and the values presented in Table 6.

From Fig. 15, it is possible to see that in mode 3 a high voltage gain is achieved at both low and high  $K$  values, that is, the converter operates with a symmetric voltage gain relation. For modes 1 and 2, on the other hand, a discontinuity is observed when  $K = 0.5$  which is where the converter moves from a quadratic to a double voltage gain relation.

### A. INTERLEAVED MODE

To evaluate the voltage gain, we perform a sweep of the parasitic resistances in the interval  $[0 \text{ } 0.6] \Omega$ , the duty-cycle at steady-state regime ( $K$ ) in the range  $[0 \text{ } 1]$ , and the load connected to the converter terminals in the interval  $[112.5 \text{ } 500] \Omega$ . According to the results, we observed two different group of effects on the voltage gain in Fig. 16.

The first group, it can be seen that the highest voltage gain is achieved when the losses  $r_{L_1}$ ,  $r_{L_2}$ ,  $r_{S_1}$  and  $r_{S_2}$  are negligible, the load demand ( $1/R$ ) is low and  $K$  is around of 90%, however increasing the losses, moving  $K$  far from 90% or reducing the load demand the voltage gain is reduced. Otherwise, on second group, the voltage gain is not much affected when the losses  $r_{C_1}$ ,  $r_{C_2}$ ,  $r_{D_1}$  and  $r_{D_2}$  are in the aforementioned range. In other words, for this case, the duty-cycle  $K$  impacts much more the voltage gain than the losses on the capacitors and diodes ( $r_{C_1}$ ,  $r_{C_2}$ ,  $r_{D_1}$  and  $r_{D_2}$ ).

### B. COMPLEMENTARY OPERATION MODE

To evaluate the voltage gain for the complementary mode, we followed the same procedure described in the previous section for the interleaved mode. However, the load sweep is now performed according to the interval  $[112.5 \text{ } 500] \Omega$ .

The results obtained for the complementary mode are presented in Fig. 17, and now three different group of effects were observed.

**FIGURE 11.** Scenario 1-The inductors current  $i_{L1}$ ,  $i_{L2}$  and voltage output  $v_o$  under steady-state condition. The solid blue line is the model response, while the red dashed line is the switched simulation. The solid blue and red dashed lines are the driving signals  $k_1$  and  $k_2$ , respectively.

**FIGURE 12.** Scenario 2-The inductors current  $i_{L1}$ ,  $i_{L2}$  and voltage output  $v_o$  under steady-state condition. The solid blue line is the model response, while the red dashed line is the switched simulation. The solid blue and red dashed lines are the driving signals  $k_1$  and  $k_2$ , respectively.

In the first group, a high voltage gain is achieved by either reducing  $r_{L1}$  and  $r_{S1}$  or moving the duty-cycle  $K$  to approximately 5% or 95%, however the highest voltage gain is obtained when  $K$  is close to 95%. In the second group,

the effect is similar. The highest voltage gain is obtained by either reducing  $r_{L2}$  and  $r_{S2}$  or moving the duty-cycle  $K$  to approximately 5% or 95%, however now the maximum gain is achieved when  $K$  is close to 5%. On the other hand, a third

**FIGURE 13.** Scenario 3-The inductors current  $i_{L1}$ ,  $i_{L2}$  and voltage output  $v_o$  under steady-state condition. The solid blue line is the model response, while the red dashed line is the switched simulation. The solid blue and red dashed lines are the driving signals  $k_1$  and  $k_2$ , respectively.

**FIGURE 14.** Scenario 4-The inductors current  $i_{L1}$ ,  $i_{L2}$  and voltage output  $v_o$  under steady-state condition. The solid blue line is the model response, while the red dashed line is the switched simulation. The solid blue and red dashed lines are the driving signals  $k_1$  and  $k_2$ , respectively.

group is observed, in which the maximum gain is achieved by reducing either  $r_{C_1}$ ,  $r_{C_2}$ ,  $r_{D_1}$  or  $r_{D_2}$ , or even by choosing  $K$  as either 5% or 95%. In this type of procedure, the highest voltage gain is quite similar in both operating points (5% and 95%).

In the latest group of effects, it can be seen that a high load demand ( $1/R$ ) reduces the voltage gain, while changing

$K$  leads to two equivalent maximum points at 5% and 95%, respectively.

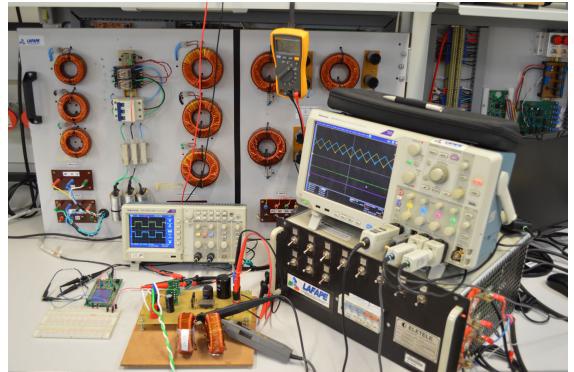

## VIII. EXPERIMENTAL RESULTS

A prototype converter from Fig. 1 was built with the devices shown in Table 11 and parameters shown

**FIGURE 15.** Behavior of the voltage gain.

in Table 12. The switching frequency was set to 10 kHz and the voltage input to 30 V. A picture of the experimental setup used to verify the effectiveness of the obtained non-ideal voltage gain and efficiency is presented in Fig. 18.

A series of experimental tests were performed to verify the effectiveness of the analytical models presented

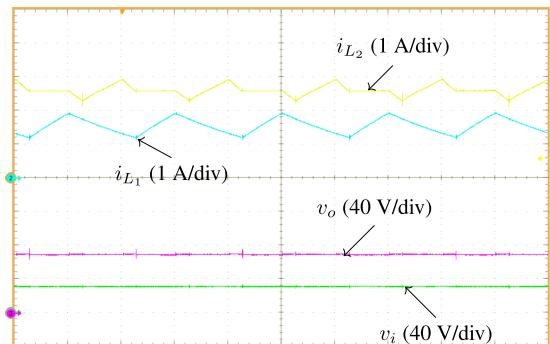

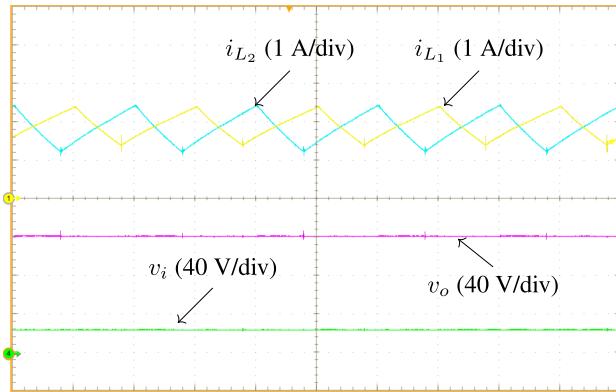

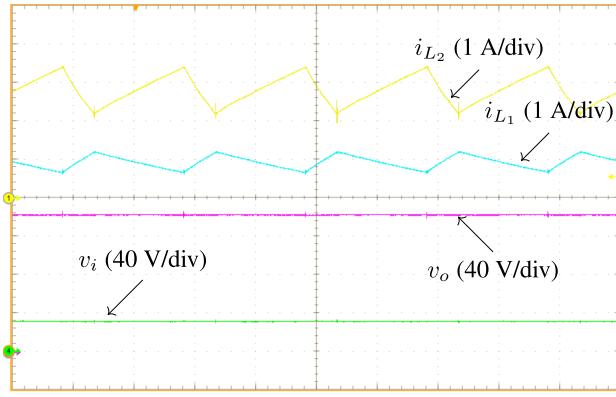

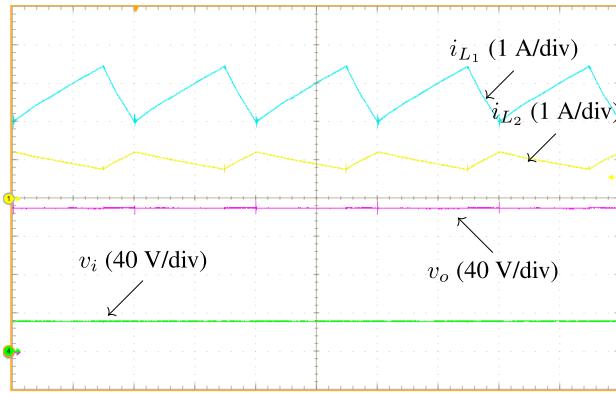

previously. The results are given in Figs. 19, 20, 21 and 22 for the same scenarios that were simulated in the Matlab/Simulink environment. It is easy to see that the experimental results match precisely in terms of behavior (shaping, level, distortion, etc) with the simulation results in Figs. 11, 12, 13 and 14.

Additionally, Table 13 shows the average current ( $I_{L1}$  and  $I_{L2}$ ) through the inductors  $L_1$  and  $L_2$ , the input ( $V_i$ ) and output ( $V_o$ ) voltages in all scenarios, while Table 14 shows the input ( $P_i$ ) and output ( $P_o$ ) power, voltage gain and efficiency ( $\eta$ ).

Other important result is achieved when Tables 9 and 10 are compared to Tables 13 and 14. Considering the output ( $V_o$ ) average voltages, the maximum relative error between the experimental and simulation results is 1.16%. Furthermore, evaluating the efficiency and the voltage gain, the greatest relative error is 0.77%.

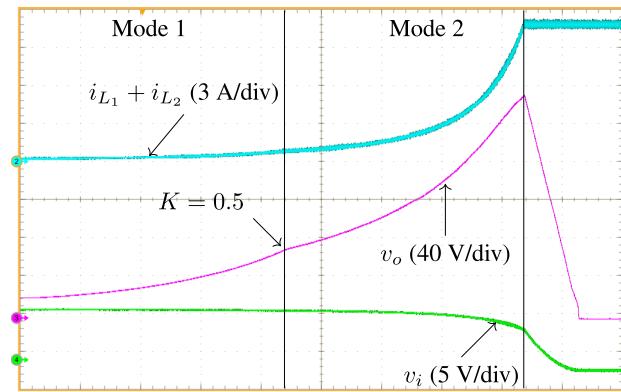

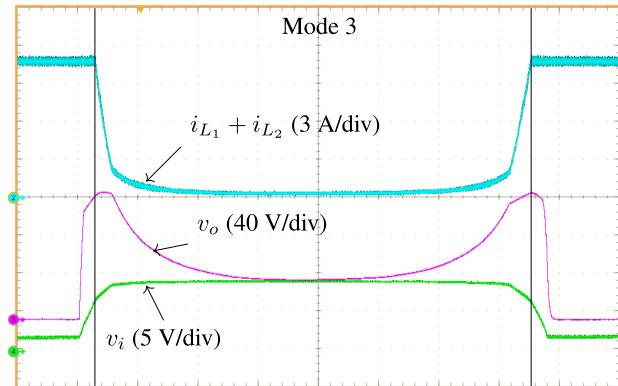

To obtain the experimental voltage gain, we performed a duty-cycle ( $K$ ) sweep in all operation modes 1, 2 and 3. The results are shown in Figs. 23 and 24. As can be noted, the limit of operation occurs when the current reaches approximately 11 A, which is the current level that leads

**FIGURE 16.** Evaluation of the voltage gain and efficiency in terms of parasitic resistances, load demand and duty-cycle for modes 1 and 2 (Interleaved mode).

**FIGURE 17.** Evaluation of the voltage gain and efficiency in terms of parasitic resistances, load and duty-cycle for mode 3 (complementary switching mode).

**TABLE 11.** Description of the commercial devices used in the cIBVM converter prototype.

| Device     | Description               |

|------------|---------------------------|

| $S_1, S_2$ | MOSFET IRF4668PbF         |

| $D_1, D_2$ | DSEI 2X31-06C             |

| $L_1, L_2$ | 3F3 ferrite grade, 18 AWG |

| $C_1, C_2$ | Electrolytic capacitors   |

**TABLE 12.** Parameters of the commercial devices used in the cIBVM converter prototype.

| Parameter              | Value               | Parameter                  | Value             |

|------------------------|---------------------|----------------------------|-------------------|

| $N_1, N_2$             | 150                 | $\hat{S}_1, \hat{S}_2$     | 6 cm <sup>2</sup> |

| $\alpha_1, \alpha_2$   | 1.31                | $\beta_1, \beta_2$         | 2.9               |

| $\hat{v}_1, \hat{v}_2$ | 151 cm <sup>3</sup> | $\lambda_1, \lambda_2$     | 17.26             |

| $r_{S_1}, r_{S_2}$     | 8 m $\Omega$        | $Q_{g_1}, Q_{g_2}$         | 161 nC            |

| $t_{r_1}, t_{r_2}$     | 105 ns              | $t_{f_1}, t_{f_2}$         | 74 ns             |

| $r_{D_1}, r_{D_2}$     | 7.1 m $\Omega$      | $V_{D_1}, V_{D_2}$         | 1.01 V            |

| $Q_{r_1}, Q_{r_2}$     | 0.9 $\mu$ C         | $V_{C_{G_1}}, V_{C_{G_2}}$ | 15 V              |

| $L_1, L_2$             | 1.3 mH              | $r_{L_1}, r_{L_2}$         | 98 m $\Omega$     |

| $C_1$                  | 100 $\mu$ F         | $r_{C_1}$                  | 25 m $\Omega$     |

| $C_2$                  | 470 $\mu$ F         | $r_{C_2}$                  | 30 m $\Omega$     |

**FIGURE 18.** Experimental setup.

**FIGURE 19.** Scenario 1—Experimental analysis at steady-state regime considering  $i_{L_1}$ ,  $i_{L_2}$ ,  $v_i$  and  $v_o$ . Time-scale is 50  $\mu$ s/div.

the DC voltage source to operate under its over current protection. In Fig. 23, it is possible to see the discontinuity

between operation modes 1 and 2 when  $K = 0.5$ . In Fig. 24, the symmetric voltage gain relation of operation

**FIGURE 20.** Scenario 2-Experimental analysis at steady-state regime considering  $i_{L_1}$ ,  $i_{L_2}$ ,  $v_i$  and  $v_o$ . Time-scale is  $50 \mu\text{s}/\text{div}$ .

**FIGURE 21.** Scenario 3-Experimental analysis at steady-state regime considering  $i_{L_1}$ ,  $i_{L_2}$ ,  $v_i$  and  $v_o$ . Time-scale is  $50 \mu\text{s}/\text{div}$ .

**FIGURE 22.** Scenario 4-Experimental analysis at steady-state regime considering  $i_{L_1}$ ,  $i_{L_2}$ ,  $v_i$  and  $v_o$ . Time-scale is  $50 \mu\text{s}/\text{div}$ .

**TABLE 13.** Average values of the states currents, input and output voltages-experimental scenarios.

| Scenario | $I_{L_1}$ (A) | $I_{L_2}$ (A) | $V_o$ (V) | $V_i$ (V) |

|----------|---------------|---------------|-----------|-----------|

| 1        | 1.34          | 2.48          | 71.44     | 28.41     |

| 2        | 1.72          | 1.78          | 151.48    | 29.99     |

| 3        | 0.92          | 2.72          | 151.66    | 29.53     |

| 4        | 2.68          | 0.91          | 151.32    | 29.69     |

mode 3 is confirmed when performing the duty-cycle ( $K$ ) sweep.

**TABLE 14.** Voltage gain and efficiency-experimental scenarios.

| Scenario | $P_i$ (W) | $P_o$ (W) | Voltage Gain | $\eta$ (%) |

|----------|-----------|-----------|--------------|------------|

| 1        | 108.53    | 102.07    | 2.51         | 94.05      |

| 2        | 104.97    | 101.98    | 5.05         | 97.16      |

| 3        | 107.49    | 102.23    | 5.13         | 95.10      |

| 4        | 106.59    | 101.77    | 5.09         | 95.48      |

**FIGURE 23.** Interleaved technique-Effect of the duty-cycle sweeping on the terminal voltage ( $v_o$ ) and input current ( $i_i = i_{L_1} + i_{L_2}$ ) when the load demand is constant ( $R = 225 \Omega$ ). Time-scale is  $20 \text{ s}/\text{div}$  and the power supply had overcurrent protection.

**FIGURE 24.** Complementary switching-Effect of the duty-cycle sweeping on the terminal voltage ( $v_o$ ) and input current ( $i_i = i_{L_1} + i_{L_2}$ ) when the load demand is constant ( $R = 225 \Omega$ ). Time-scale is  $20 \text{ s}/\text{div}$  and the power supply had overcurrent protection.

## IX. CONCLUSION

In this paper, a complete non-ideal steady-state analysis of a threecold operation mode interleaved-based DC-DC converter was performed. Although the converter topology has been firstly proposed in [24], a complete description of the non-ideal performance was not deeply explored in the literature. As was previously discussed, it is possible to successfully implement three different operation modes depending solely on the switching strategy that is used. In this case, operation modes 1 and 2 are obtained when adopting the interleaved switching strategy across intervals  $0 \leq K < 0.5$  and  $0.5 \leq K \leq 1$ , thus yielding a quadratic and a double static voltage gain relation, respectively. Operation mode 3, on the other hand, is obtained upon considering a complementary

switching strategy, which leads to a high symmetric static voltage gain relation on the converter terminals.

As an inherent drawback, it was shown that both the complementary mode and the interleaved mode with  $K < 0.5$  the inductor currents are imbalanced. On the other hand, in such regions the converter exhibits unique characteristics as symmetric and quadratic voltage gain, which results in a trade-off to be faced and dealt with by designers.

The performed non-ideal analyzes were entirely based on the state-space models, with conduction and dynamic losses, which were calculated for each specific operation mode, besides presenting a complete evaluation of the static voltage gain and efficiency relations. It was also presented a detailed description of each resistive loss impact in terms of overall performance.

Finally, a Simulink-based cross validation and a sequence of experimental tests were carried out to validate the obtained models. The results showed that the calculated analytical models are effective, since it is possible to observe that the plotted and experimental waveforms match precisely in terms of shape, level and distortion. Nevertheless, it is important to state that when the experimental results are confronted against the simulation, a overall mean relative error of 1.78% is observed, which is a reasonable approximation.

## REFERENCES

- [1] M. Lakshmi and S. Hemamalini, "Nonisolated high gain DC-DC converter for DC microgrids," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1205–1212, Feb. 2018.

- [2] C. R. de Aguiar, G. H. F. Fuzato, R. F. Q. Magossi, R. V. A. Neves, and R. Q. Machado, "A new method to manage the fuel cell initialization," *IEEE Trans. Ind. Appl.*, vol. 54, no. 5, pp. 5187–5195, Sep. 2018.

- [3] G. H. F. Fuzato, C. R. Aguiar, R. F. Bastos, and R. Q. Machado, "Evaluation of an interleaved boost converter powered by fuel cells and connected to the grid via voltage source inverter," *IET Power Electron.*, vol. 11, no. 10, pp. 1661–1672, Aug. 2018.

- [4] W. Yu, H. Qian, and J. S. Lai, "Design of high-efficiency bidirectional DC-DC converter and high-precision efficiency measurement," *IEEE Trans. Power Electron.*, vol. 25, no. 3, pp. 650–658, Oct. 2010.

- [5] H. Moradisizkoohi, N. Elsayad, and O. A. Mohammed, "Experimental demonstration of a modular, quasi-resonant bidirectional DC-DC converter using GaN switches for electric vehicles," *IEEE Trans. Ind. Appl.*, vol. 55, no. 6, pp. 7787–7803, Nov. 2019.

- [6] M. Uno, M. Inoue, Y. Sato, and H. Nagata, "Bidirectional interleaved PWM converter with high voltage-conversion ratio and automatic current balancing capability for single-cell battery power system in small scientific satellites," *Energies*, vol. 11, no. 10, p. 2702, Oct. 2018.

- [7] N. Lee, J.-Y. Lee, Y.-J. Cheon, S.-K. Han, and G.-W. Moon, "A high-power-density converter with a continuous input current waveform for satellite power applications," *IEEE Trans. Ind. Electron.*, vol. 67, no. 2, pp. 1024–1035, Feb. 2020.

- [8] V. Dargahi, A. K. Sadigh, M. Abarzadeh, S. Eskandari, and K. A. Corzine, "A new family of modular multilevel converter based on modified flying-capacitor multicell converters," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 138–147, Jan. 2015.

- [9] V. F. Pires, A. Cordeiro, D. Foito, and J. F. Silva, "High step-up DC-DC converter for fuel cell vehicles based on merged quadratic Boost-Cuk," *IEEE Trans. Veh. Technol.*, vol. 68, no. 8, pp. 7521–7530, Aug. 2019.

- [10] C.-S. Wang, S.-H. Zhang, Y.-F. Wang, B. Chen, and J.-H. Liu, "A 5-kW isolated high voltage conversion ratio bidirectional CLTC resonant DC-DC converter with wide gain range and high efficiency," *IEEE Trans. Power Electron.*, vol. 34, no. 1, pp. 340–355, Jan. 2019.

- [11] R. Giral, L. Martinez-Salamero, and S. Singer, "Interleaved converters operation based on CMC," *IEEE Trans. Power Electron.*, vol. 14, no. 4, pp. 643–652, Jul. 1999.

- [12] M. Muhammad, M. Armstrong, and M. A. Elgendy, "A nonisolated interleaved boost converter for high-voltage gain applications," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 2, pp. 352–362, Jun. 2016.

- [13] P.-W. Lee, Y.-S. Lee, D. K. W. Cheng, and X.-C. Liu, "Steady-state analysis of an interleaved boost converter with coupled inductors," *IEEE Trans. Ind. Electron.*, vol. 47, no. 4, pp. 787–795, Aug. 2000.

- [14] A. Khosroshahi, M. Abapour, and M. Sabahi, "Reliability evaluation of conventional and interleaved DC-DC boost converters," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5821–5828, Oct. 2015.

- [15] S. V. Dhople, A. Davoudi, A. D. Domínguez-García, and P. L. Chapman, "A unified approach to reliability assessment of multiphase DC-DC converters in photovoltaic energy conversion systems," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 739–751, Feb. 2012.

- [16] G. H. F. Fuzato, K. D. A. Ottoboni, R. F. Bastos, C. R. Aguiar, and R. Q. Machado, "Voltage gain analysis of the interleaved boost with voltage multiplier converter used as electronic interface for fuel cells systems," *IET Power Electron.*, vol. 9, no. 9, pp. 1842–1851, Jul. 2016.

- [17] C. Schaeff and J. T. Stauth, "A 3-Phase resonant switched capacitor converter delivering 7.7 w at 85% efficiency using 1.1 nH PCB trace inductors," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2861–2869, Dec. 2015.

- [18] Y. Ahn, I. Jeon, and J. Roh, "A multiphase buck converter with a rotating phase-shedding scheme for efficient light-load control," *IEEE J. Solid-State Circuits*, vol. 49, no. 11, pp. 2673–2683, Nov. 2014.

- [19] K. I. Hwu, W. Z. Jiang, and P. Y. Wu, "An expandable four-phase interleaved high step-down converter with low switch voltage stress and automatic uniform current sharing," *IEEE Trans. Ind. Electron.*, vol. 63, no. 10, pp. 6064–6072, Oct. 2016.

- [20] O. Hegazy, J. V. Mierlo, and P. Lataire, "Analysis, modeling, and implementation of a multidevice interleaved DC/DC converter for fuel cell hybrid electric vehicles," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4445–4458, Nov. 2012.

- [21] Y. Zheng and K. M. Smedley, "Interleaved high step-up converter integrating coupled inductor and switched capacitor for distributed generation systems," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7617–7628, Aug. 2019.

- [22] L. C. Franco, L. L. Pfitscher, and R. Gules, "A new high static gain nonisolated DC-DC converter," in *Proc. IEEE 34th Annu. Conf. Power Electron. Spec. (PESC)*, vol. 3, Jun. 2003, pp. 1367–1372.

- [23] R. Gules, L. L. Pfitscher, and L. C. Franco, "An interleaved boost DC-DC converter with large conversion ratio," in *Proc. IEEE Int. Symp. Ind. Electron.*, vol. 1, Jun. 2003, pp. 411–416.

- [24] L.-W. Zhou, B.-X. Zhu, and Q.-M. Luo, "High step-up converter with capacity of multiple input," *IET Power Electron.*, vol. 5, no. 5, p. 524, 2012.

- [25] Z. Ivanovic, B. Blanusa, and M. Knezic, "Analytical power losses model of boost rectifier," *IET Power Electron.*, vol. 7, no. 8, pp. 2093–2102, Aug. 2014.

- [26] I. Endo, H. Tatsumi, I. Otsuka, H. Yamamoto, A. Shintani, H. Koshimoto, M. Yagi, and K. Murata, "Magnetic properties of compressed amorphous powder cores and their application to a fly-back converter," *IEEE Trans. Magn.*, vol. 36, no. 5, pp. 3421–3423, Sep. 2000.

- [27] A. Ayachit and M. K. Kazimierczuk, "Averaged small-signal model of PWM DC-DC converters in CCM including switching power loss," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 2, pp. 262–266, Feb. 2019.

- [28] M. Orabi and A. Shawky, "Proposed switching losses model for integrated Point-of-Load synchronous buck converters," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 5136–5150, Sep. 2015.

- [29] Y. Xiong, S. Sun, H. Jia, P. Shea, and Z. J. Shen, "New physical insights on power MOSFET switching losses," *IEEE Trans. Power Electron.*, vol. 24, no. 2, pp. 525–531, Feb. 2009.

**RAFAEL FERNANDO QUIRINO MAGOSSI**

(Member, IEEE) received the B.Eng. and M.Sc. degrees in electrical engineering from the University of São Paulo, São Carlos, Brazil, in 2016 and 2018, respectively, where he is currently pursuing the Ph.D. degree. Since 2018, he has been a Professor with the Federal Center for Technological Education (CEFET/RJ), Rio de Janeiro, Brazil. His research interests include control systems, power electronics, and renewable power systems.

**DANIEL SILVA DE CASTRO** was born in João Monlevade, Brazil. He received the B.Eng. degree in electrical engineering from the Federal University of Ouro Preto, João Monlevade, in 2018. He is currently pursuing the M.Sc. degree in electrical engineering with the University of São Paulo. Since 2019, he has been a Design Engineer of the Electronics and Controls Team, Tecumseh Products Company LLC. His research interests include analysis and design of new power converters, the digital control of power electronic devices and electric machines, microgrids, and the real-time simulation of dynamic systems.

**RICARDO QUADROS MACHADO** (Senior Member, IEEE) was born in Santa Maria, Brazil. He received the B.S. degree from the University of Santa Maria, Santa Maria, Brazil, in 1997, and the M.S. and Ph.D. degrees in electrical engineering from the University of Campinas, Campinas, Brazil, in 2000 and 2005, respectively. From 2002 to 2003, he was a Visiting Researcher at the University of Padova, Padova, Italy, and from 2005 to 2007, he was a Postdoctoral Fellow of the Federal University of Santa Maria. From 2013 to 2014, he was a Visiting Professor at the University of Toronto, Toronto, Canada. In addition, he was an Assistant Professor with the University of São Paulo, São Carlos, Brazil, from 2007 to 2018. He is currently an Associate Professor with the University of São Paulo. His main research interests are in the processing of energy in dc–dc and dc–ac converters, the digital control of power converters, distributed generation systems, smart grids, and the control of renewable energy sources.

**ANA LAÍS RUI OLIVEIRA** received the degree in electrical engineering from the University of São Paulo, São Carlos, in 2019. Her research interests include renewable energy sources, power systems, and dc–dc power converters. She is currently working at Synchro, Campinas, Brazil, as a DevOps Analyst and also a collaborative Researcher in LAFAPE at the University of São Paulo.